- 您现在的位置:买卖IC网 > PDF目录9003 > MPC9773AER2 (IDT, Integrated Device Technology Inc)IC PLL CLK GEN 1:12 3.3V 52-LQFP PDF资料下载

参数资料

| 型号: | MPC9773AER2 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 21/21页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLK GEN 1:12 3.3V 52-LQFP |

| 标准包装: | 1,500 |

| 类型: | PLL 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVPECL |

| 输出: | LVCMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 3:12 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 242.5MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 52-LQFP |

| 供应商设备封装: | 52-TQFP(10x10) |

| 包装: | 带卷 (TR) |

MPC9773 REVISION 6 JANUARY 31, 2013

9

2013 Integrated Device Technology, Inc.

MPC9773 Data Sheet

3.3 V 1:12 LVCMOS PLL CLOCK GENERATOR

APPLICATIONS INFORMATION

MPC9773 Configurations

Configuring the MPC9773 amounts to properly configuring

the internal dividers to produce the desired output

frequencies. The output frequency can be represented by

this formula:

where fREF is the reference frequency of the selected input

clock source (CCLKO, CCLK1 or PCLK), M is the PLL

feedback divider and N is an output divider. The PLL

feedback divider is configured by the FSEL_FB[2:0] and the

output dividers are individually configured for each output

bank by the FSEL_A[1:0], FSEL_B[1:0] and FSEL_C[1:0]

inputs.

The reference frequency fREF and the selection of the

feedback-divider M is limited by the specified VCO frequency

range. fREF and M must be configured to match the VCO

frequency range of 200 to 480 MHz in order to achieve stable

PLL operation:

fVCO,MIN (fREF VCO_SEL M) fVCO,MAX

The PLL post-divider VCO_SEL is either a divide-by-one

or a divide-by-two and can be used to situate the VCO into

the specified frequency range. This divider is controlled by

the VCO_SEL pin. VCO_SEL effectively extends the usable

input frequency range while it has no effect on the output to

reference frequency ratio.

The output frequency for each bank can be derived from

the VCO frequency and output divider:

fQA[0:3] = fVCO (VCO_SEL NA)

fQB[0:3] = fVCO (VCO_SEL NB)

fQC[0:3] = fVCO (VCO_SEL NC)

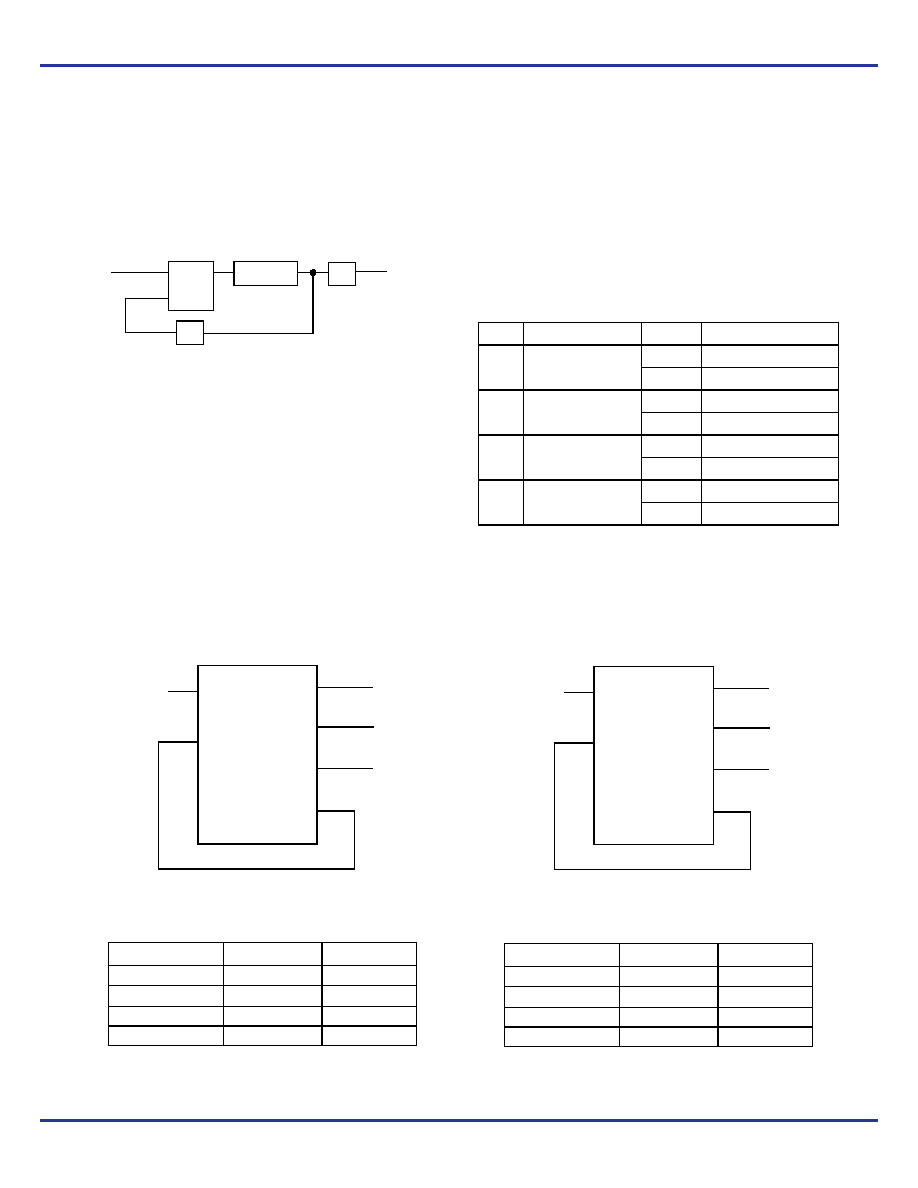

Table 11 shows the various PLL feedback and output

configurations for the MPC9773.

Figure 3. Example Configuration

Figure 4. Example Configuration

VCO_SEL

M

N

fREF

fOUT

fOUT = fREF M N

PLL

Table 11. MPC9773 Divider

Divider

Function

VCO_SEL

Values

M

PLL Feedback

FSEL_FB[0:3]

1

4, 6, 8, 10, 12, 16

2

8, 12, 16, 20, 24, 32, 40

NA

Bank A Output

Divider FSEL_A[0:1]

1

4, 6, 8, 12

2

8, 12, 16, 24

NB

Bank B Output

Divider FSEL_B[0:1]

1

4, 6, 8, 10

2

8, 12, 16, 20

NC

Bank C Output

Divider FSEL_C[0:1]

1

2, 4, 6, 8

2

4, 8, 12, 16

MPC9773

fREF = 33.3 MHz

33.3 MHz

100 MHz

33.3 MHz (Feedback)

200 MHz

CCLK0

VCO_SEL

FSEL_A[1:0]

FSEL_B[1:0]

FSEL_C[1:0]

FSEL_FB[2:0]

QA[3:0]

QB[3:0]

QC[3:0]

QFB

CCLK1

CCLK_SEL

FB_IN

1

11

00

101

MPC9773 example configuration (feedback of

QFB = 33.3 MHz, fVCO = 400 MHz, VCO_SEL = 1,

M = 12, NA = 12, NB = 4, NC = 2).

Frequency Range

Min

Max

Input

16.6 MHz

40 MHz

QA outputs

16.6 MHz

40 MHz

QB outputs

50 MHz

120 MHz

QC outputs

100 MHz

240 MHz

MPC9773

fREF = 25 MHz

62.5 MHz

25 MHz (Feedback)

125 MHz

CCLK0

VCO_SEL

FSEL_A[1:0]

FSEL_B[1:0]

FSEL_C[1:0]

FSEL_FB[2:0]

QA[3:0]

QB[3:0]

QC[3:0]

QFB

CCLK1

CCLK_SEL

FB_IN

1

00

011

MPC9773 example configuration (feedback of

QFB = 25 MHz, fVCO = 250 MHz, VCO_SEL = 1,

M = 10, NA = 4, NB = 4, NC = 2).

Frequency Range

Min

Max

Input

20 MHz

48 MHz

QA outputs

50 MHz

120 MHz

QB outputs

50 MHz

120 MHz

QC outputs

100 MHz

240 MHz

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B4D-MY-F2 | CONVERTER MOD DC/DC 85V 50W |

| VE-B4D-MY-F1 | CONVERTER MOD DC/DC 85V 50W |

| MS27473T24F2S | CONN PLUG 100POS STRAIGHT W/SCKT |

| VE-BNL-MV-F1 | CONVERTER MOD DC/DC 28V 150W |

| VE-BNK-MV-F4 | CONVERTER MOD DC/DC 40V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC9773FA | 功能描述:锁相环 - PLL 3.3V 240MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| MPC9773FAR2 | 制造商:Integrated Device Technology Inc 功能描述:PLL Clock Driver Single 52-Pin LQFP T/R 制造商:Integrated Device Technology Inc 功能描述:MPC9773FAR2 - Tape and Reel |

| MPC9774 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:3.3V / 2,5V 1:14 LVCMOS PLL CLOCK GENERATOR |

| MPC9774AE | 功能描述:时钟发生器及支持产品 3.3V 125MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9774AER2 | 功能描述:IC PLL CLK GEN 1:14 3.3V 52-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。