- 您现在的位置:买卖IC网 > PDF目录9591 > MPC9850VMR2 (IDT, Integrated Device Technology Inc)IC PLL CLOCK GENERATOR 100MAPBGA PDF资料下载

参数资料

| 型号: | MPC9850VMR2 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 10/12页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLOCK GENERATOR 100MAPBGA |

| 标准包装: | 1,000 |

| 类型: | 时钟/频率发生器,多路复用器 |

| PLL: | 是 |

| 主要目的: | 联网,PowerQUICC III,电信 |

| 输入: | LVCMOS,LVPECL,晶体 |

| 输出: | LVCMOS,LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 3:11 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 500MHz |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 100-LBGA |

| 供应商设备封装: | 100-CABGA(11x11) |

| 包装: | 带卷 (TR) |

MPC9850 Data Sheet

Clock Generator for PowerQUICC III

MPC9850 REVISION 6 FEBRUARY 6, 2013

7

2013 Integrated Device Technology, Inc.

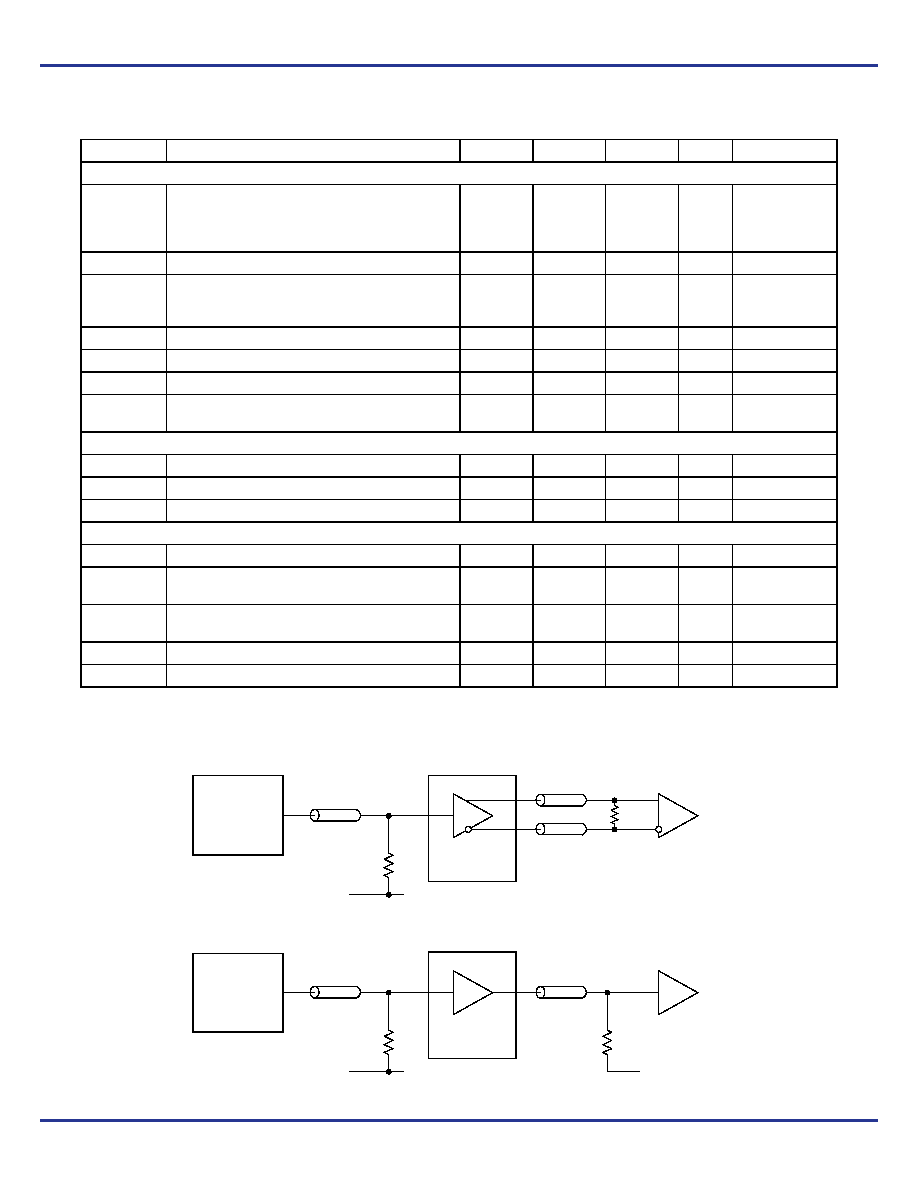

Figure 4. MPC9850 AC Test Reference (LVDS Outputs)

Figure 5. MPC9850 AC Test Reference (LVCMOS Outputs)

Table 11. AC Characteristics (VDD = 3.3 V ± 5%, VDDOA = 3.3 V ± 5%,VDDOB = 3.3 V ± 5%, TA= –40°C to +85°C)(1) (2)

1. AC characteristics are design targets and pending characterization.

2. AC characteristics apply for parallel output termination of 50

to VTT.

Symbol

Characteristics

Min

Typ

Max

Unit

Condition

Input and Output Timing Specification

fref

Input Reference Frequency (25 MHz input)

Input Reference Frequency (33 MHz input)

XTAL Input

Input Reference Frequency in PLL Bypass Mode(3)

3. In bypass mode, the MPC9850 divides the input reference clock.

25

33

25

250

MHz

PLL bypass

fVCO

VCO Frequency Range(4)

4. The input reference frequency must match the VCO lock range divided by the total feedback divider ratio: fref = (fVCO M) N.

2000

MHz

fMCX

Output Frequency

Bank A output

Bank B output

Bank C output

15.87

50

200

500

MHz

PLL locked

frefPW

Reference Input Pulse Width

2

ns

frefCcc

Input Frequency Accuracy

100

ppm

tr, tf

Output Rise/Fall Time

150

500

ps

20% to 80%

DC

Output Duty Cycle

43

47

50

57

53

%

Bank A and B

Bank C

PLL Specifications

tLOCK

Maximum PLL Lock Time

10

ms

treset_ref

MR Hold Time on Power Up

10

ns

treset_pulse

MR Hold Time

10

ns

Skew and Jitter Specifications

tsk(O)

Output-to-Output Skew (within a bank)

50

ps

tsk(O)

Output-to-Output Skew (across banks A and B)

400

ps

VDDOA = 3.3 V

VDDOB = 3.3 V

tJIT(CC)

Cycle-to-Cycle Jitter

200

150

ps

Bank A and B

Bank C

tJIT(PER)

Period Jitter

200

ps

Bank A and C

tJIT()

I/O Phase Jitter

RMS (1

)

50

ps

Bank A and C

Pulse

Generator

Z = 50

RT = 50

ZO = 50

DUT MPC9850

VTT

RT = 100

ZO = 50

Pulse

Generator

Z = 50

RT = 50

ZO = 50

DUT MPC9850

VTT

ZO = 50

RT = 50

VTT

相关PDF资料 |

PDF描述 |

|---|---|

| CY2SSTV857ZXC-32T | IC CLK DDR266/333BUF1:10 48TSSOP |

| ICS9DB202CFLFT | IC JITTER ATTENUATOR 20-SSOP |

| MS3128F16-26P | CONN RCPT 26POS WALL MNT W/PINS |

| MS3128F14-12S | CONN RCPT 12POS WALL MNT W/SCKT |

| SL28504BZI-2T | IC CLOCK GEN EAGLELAKE 56TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC9855 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:Clock Generator for PowerQUICC and PowerPC Microprocessors |

| MPC9855VM | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9855VMR2 | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9865VM | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9865VMR2 | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。