- 您现在的位置:买卖IC网 > PDF目录45594 > MUPA64K16-15TJI SPECIALTY MICROPROCESSOR CIRCUIT, PQFP128 PDF资料下载

参数资料

| 型号: | MUPA64K16-15TJI |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP128 |

| 封装: | LQFP-128 |

| 文件页数: | 12/19页 |

| 文件大小: | 380K |

| 代理商: | MUPA64K16-15TJI |

MUPA64K16 Alto Priority Queue Scheduler

MUSIC Semiconductors Confidential

2

Rev 0.3 Draft

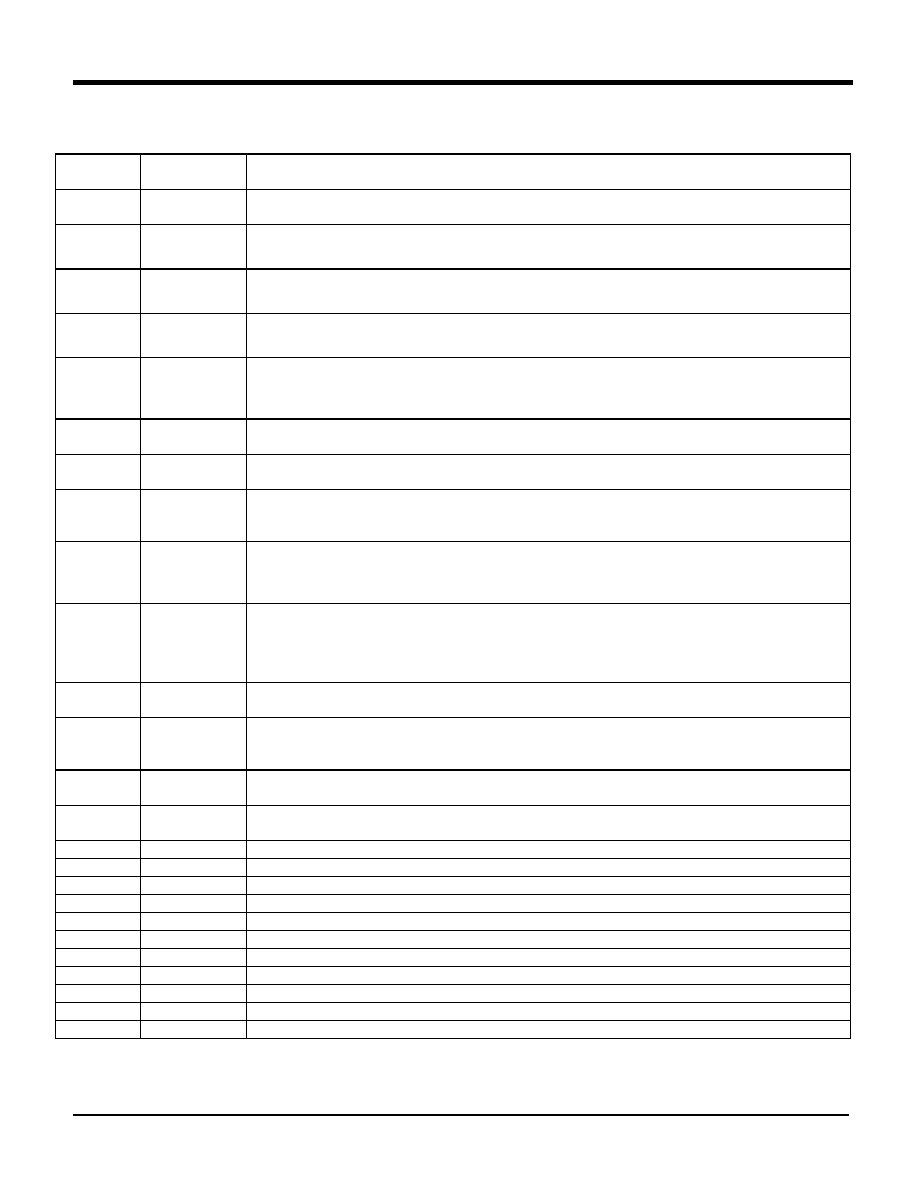

Table 1: Pin Description

Signal

Name

Function

REG[2.0]

Input

Register Select. Selects the register to be read or written during a DQ[31:0] bus

operation.

OP[2:0]

Input

Instruction Bus OP[2:0] selects the operation to be performed. See Table 5 showing op

codes for a list of legal values.

PQ[3.0]

Input

Priority Queue Select. Selects the priority queue to which an operation applied. Note

that some operations, such as Noop, do not use this value.

/W

Input

Read/Write. /W enables a register write or an operation that inputs data, such as Insert,

depending on the value of OP[2:0].

/CS

Input

Chip Select. /CS indicates to the device that a new command is available on OP[2:0],

REG[2:0], PQ[3:0] and /W. If /W is zero, then /CS also indicates that there is new data

on the DQ[31:0]. /CS must be synchronous to CLK.

STR[4:0]

Output

Status Register. Provides device status information; equivalent to bits 4:0 of the Status

Register (see Table 2).

CLK

Input

Device clock. All internal operations and interface timings are synchronized to the rising

edge of the clock.

/RST

Input

System Reset. The PLL in Alto requires 100 microseconds to stabilize after reset and

no commands should be issued during this time. Also, the UID manager requires an

additional 2200 clock cycles to initialize after this 100 microsecond interval.

AD[15:0]

Output

Associated Data Bus. This bus outputs the associated data for interface to external

RAM. The contents of both the IDR and MDR are made available on this bus, selected

by ADS.

/ADV

Output

Associated Data Bus Valid. ADV indicates the validity of the AD[15:0] bus. AD[15:0] is

invalid when ADS=1 and a peek or extract operation is performed on an empty priority

queue. /ADV signal is an address bit AD[16] of the Associated Data Bus, however,

AD[16] is not a part of the SRAM address.

ADS

Input

Associated Data Bus Select. ADS determines whether the AD[15:0] bus carries the

value of the IDR (ADS=0) or the MDR (ADS=1).

/ADOE

Input

Associated Data Bus Output Enable. /ADOE asynchronously enables Alto to drive the

AD[15:0] bus.

DQ[31:0]

Input/Output

Data Bus. The bi-directional data bus writes to and reads from the registers. Data for

registers that are less than 32 bits occupy the least significant bits of DQ[31:0].

/DQOE

Input

Data Bus Output Enable. Asynchronously enables the device to drive the DQ[31:0]

pins.

/RDY

Input

READY. RDY indicates that the bus is idle and able to accept a new command.

/TRST

Input

JTAG reset pin.

TCLK

Input

JTAG Test Clock.

TMS

Input

JTAG Test Mode Select.

TDI

Input

JTAG Test data Input.

TDO

Output

JTAG Test Data Output.

VDD

Power

Supply Voltage for Core (1.8V)

VDDQ

Power

Supply Voltage for I/O (3.3V)

VSS

GND

Ground

AVDD

Input

Supply Voltage for PLL (1.8V)

AVSS

GND

Ground for PLL

相关PDF资料 |

PDF描述 |

|---|---|

| MUR1005FCT | 10 A, 50 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1020FCT | 10 A, 200 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1030FCT | 10 A, 300 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1040FCT | 10 A, 400 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1005FCTP | 10 A, 50 V, SILICON, RECTIFIER DIODE, TO-220AB |

相关代理商/技术参数 |

参数描述 |

|---|---|

| mur | 制造商:Datak Corporation 功能描述: |

| MUR 120G | 制造商:ON Semiconductor 功能描述:Bulk |

| MUR 3 | 制造商:Crouzet 功能描述:Bulk |

| MUR 3020WTPBF | 制造商:Vishay 功能描述:Bulk |

| MUR 4100EG | 制造商:ON Semiconductor 功能描述:Bulk |

发布紧急采购,3分钟左右您将得到回复。