- 您现在的位置:买卖IC网 > PDF目录45594 > MUPA64K16-15TJI SPECIALTY MICROPROCESSOR CIRCUIT, PQFP128 PDF资料下载

参数资料

| 型号: | MUPA64K16-15TJI |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP128 |

| 封装: | LQFP-128 |

| 文件页数: | 4/19页 |

| 文件大小: | 380K |

| 代理商: | MUPA64K16-15TJI |

MUPA64K16 Alto Priority Queue Scheduler

MUSIC Semiconductors Confidential

12

Rev 0.3 Draft

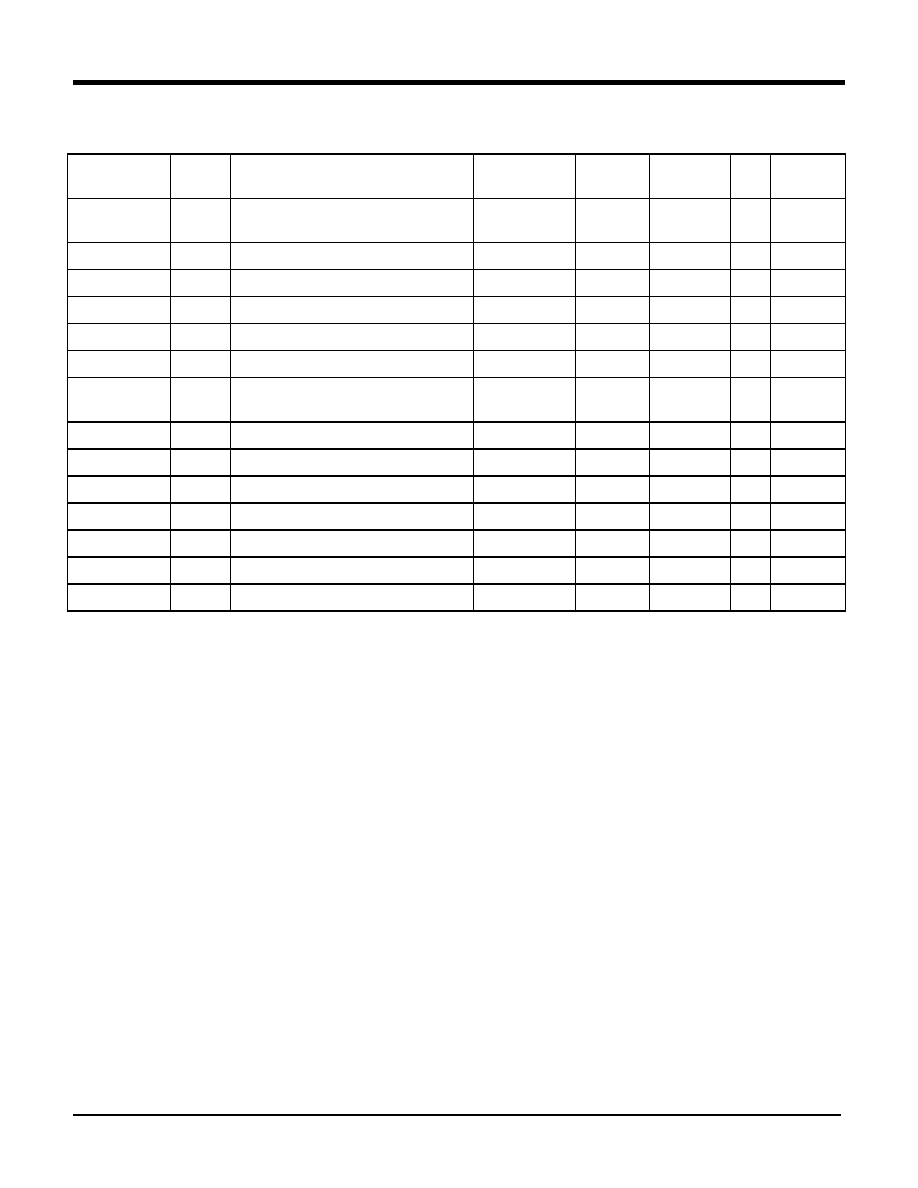

Table 13: Pipeline Instructions

Pipeline

Cycle

Clock

Cycle

Operation

Instruction

OP[2:0]

REG[2:0]

/W

PQ[3:0]

P

1

Read UGR, Start UID Get (9

clocks)

UID Get

5

1

N

P-1

4

Wait for Both to complete

P-1

7

Read MDR

Noop

0

1

N/A

P-1

10

Read MKR (if desired)

Noop

0

1

N/A

P

13

Write IKR

Noop

0

N/A

P

15

Write IDR, start Both (10 clocks)

Both

3

1

0

N

P-1

17

Write UPR, Start UID Put (3

clocks

UID Put

6

0

N/A

P+1

19

Read UGR, Start UID Get

UID Get

5

1

N

P

22

Wait for Both to complete

P

25

Read MDR

Noop

0

1

N/A

P

28

Read MKR (if desired)

Noop

0

1

N/A

P+1

31

Write IKR

Noop

0

N/A

P+1

33

Write IDR, start Both (10 clocks)

Both

3

1

0

N

P

35

Write UPR, Start UID Put

UID Put

6

0

N/A

JTAG INTERFACE

This section contains the Test Access Port and

Boundary Scan Architecture as specified by the IEEE

JTAG standard 1149.1. It consists of five JTAG

interface signals TCK, TMS, /TRST, TDI and TDO.

/TRST (JTAG Reset, Input)

/TRST is the Test Reset input.

TCLK (JTAG Test Clock, Input)

TCLK is the Test Clock input.

TMS (JTAG Test Mode Select, Input)

TMS is the Test Mode Select input.

TDI (JTAG Test Data Input, Input)

TDI is the Test Data input.

TDO (JTAG Test Data Output, Output)

TDO is the Test Data output.

相关PDF资料 |

PDF描述 |

|---|---|

| MUR1005FCT | 10 A, 50 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1020FCT | 10 A, 200 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1030FCT | 10 A, 300 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1040FCT | 10 A, 400 V, SILICON, RECTIFIER DIODE, TO-220AB |

| MUR1005FCTP | 10 A, 50 V, SILICON, RECTIFIER DIODE, TO-220AB |

相关代理商/技术参数 |

参数描述 |

|---|---|

| mur | 制造商:Datak Corporation 功能描述: |

| MUR 120G | 制造商:ON Semiconductor 功能描述:Bulk |

| MUR 3 | 制造商:Crouzet 功能描述:Bulk |

| MUR 3020WTPBF | 制造商:Vishay 功能描述:Bulk |

| MUR 4100EG | 制造商:ON Semiconductor 功能描述:Bulk |

发布紧急采购,3分钟左右您将得到回复。