- 您现在的位置:买卖IC网 > PDF目录69041 > MX98216EC (MACRONIX INTERNATIONAL CO LTD) 16 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP208 PDF资料下载

参数资料

| 型号: | MX98216EC |

| 厂商: | MACRONIX INTERNATIONAL CO LTD |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP208 |

| 封装: | PLASTIC, QFP-208 |

| 文件页数: | 20/37页 |

| 文件大小: | 269K |

| 代理商: | MX98216EC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

MX98216EC

P/N:PM0781

REV. 0.2, Apr, 18, 2001

27

their network activity or fundamental network broadcasting will not affect or get distributed across those VLAN groups

to each other.

In this way, it can reduce the need for unwanted traffic in the network.

Moreover, the

damaged/abnormal ports can be isolated by removing them from VLAN groups' list, so as to prevent network

meltdown.

Port-based VLAN in MX98216EC is also very flexible that every port can be shared by multiple groups as

the "trunk port" while the other unshared ports are remained independent.

Queue Management

MX98216EC utilizes the store-and-forward switching scheme, which needs memory for frame reception and

transmission buffering.

In MX98216EC, the embedded buffer memory is partitioned into pages which dynamically

allocates the related frame data and switching information.

The buffer management control unit dispatches pointers

pointing to those pages upon frames reception of the egress ports.

For unicast frames, the occupied buffer pages are released after the corresponding ports complete transmission.

Their pointers are returned to buffer management control unit for reuse.

For broadcast frames, the switch controller

count the times of transmission of the same broadcast frame till all ports finish the broadcast transmission, then the

occupied memory space are released to the free buffer pool.

Since there are various kinds of page/pointer requests for the buffer management, a queue manager is used in

MX98216EC to handle those access requests.

Via a proprietary arbitration method, the queue manager grants fair

enough throughput for each port to transmit at wire speed.

93C46 EEPROM Interface

Provide serial interface to load the values of external EEPROM which switch can configure in advance.

At initial

stage, switch will loads the data to internal registers and operates as expected.

Either EEPROM or CPU interface

can be used once a time.

CPU Interface

MX98216EC provides another powerful way to configure the value of register via CPU, which can access its as well as

PHY registers and the address table at any time.

Basically, MAC address look up, content of address table status

and frozen a dedicated address are the major function for CPU access through address table.

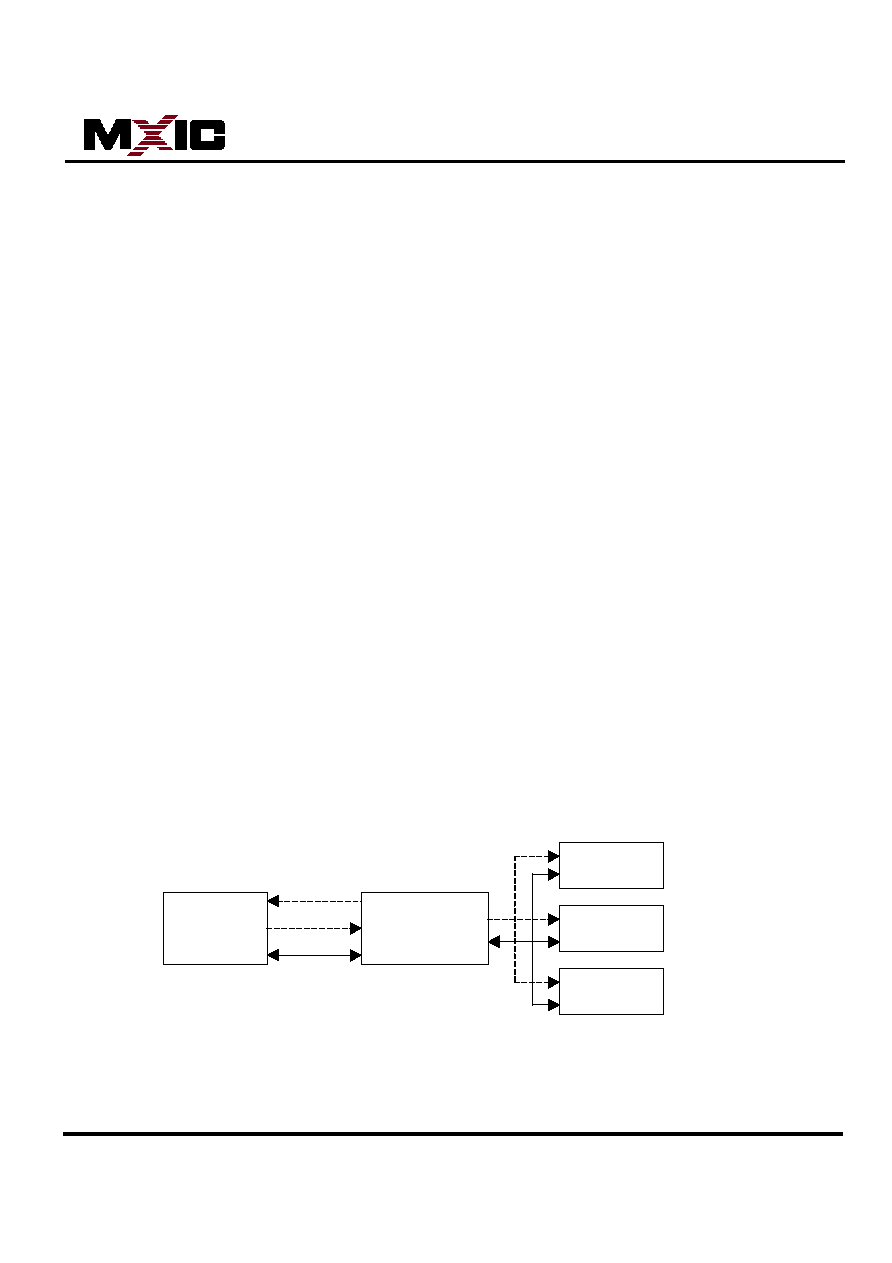

Following is the basic

system diagram for the connection of host processor, switch, and PHY.

Host

Processor

MX98216EC

Switch

Octal PHY

OUTCLK

INCLK

IODATA

MDC

MDIO

Serial Management Block Diagram via Switch and PHY

相关PDF资料 |

PDF描述 |

|---|---|

| MX98902AQC | 2 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQCC84 |

| P024T048T12AL | 1-OUTPUT 120 W DC-DC REG PWR SUPPLY MODULE |

| P048T048M12AL | 1-OUTPUT 120 W DC-DC REG PWR SUPPLY MODULE |

| P048F048M12AL | 1-OUTPUT 120 W DC-DC REG PWR SUPPLY MODULE |

| PADS1298CZXGT | SPECIALTY ANALOG CIRCUIT, PBGA64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MX98224EC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:24-port Dual-Speed Ethernet Switch Controller |

| MX98702 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:LAN Transceiver |

| MX98704 | 制造商:MCNIX 制造商全称:Macronix International 功能描述:100BASE-TX PHYSICAL DATA TRANSCEIVER |

| MX98704EC | 制造商:MCNIX 制造商全称:Macronix International 功能描述:100BASE-TX PHYSICAL DATA TRANSCEIVER |

| MX98704QC | 制造商:MCNIX 制造商全称:Macronix International 功能描述:100BASE-TX PHYSICAL DATA TRANSCEIVER |

发布紧急采购,3分钟左右您将得到回复。