- 您现在的位置:买卖IC网 > PDF目录367726 > P87C42 (INTEL CORP) UNIVERSAL PERIPHERAL INTERFACE CHMOS 8-BIT SLAVE MICROCONTROLLER PDF资料下载

参数资料

| 型号: | P87C42 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | UNIVERSAL PERIPHERAL INTERFACE CHMOS 8-BIT SLAVE MICROCONTROLLER |

| 中文描述: | 8-BIT, OTPROM, 12.5 MHz, MICROCONTROLLER, PDIP40 |

| 封装: | PLASTIC, DIP-40 |

| 文件页数: | 5/25页 |

| 文件大小: | 345K |

| 代理商: | P87C42 |

UPI-C42/UPI-L42

UPI-42 COMPATIBLE FEATURES

1.

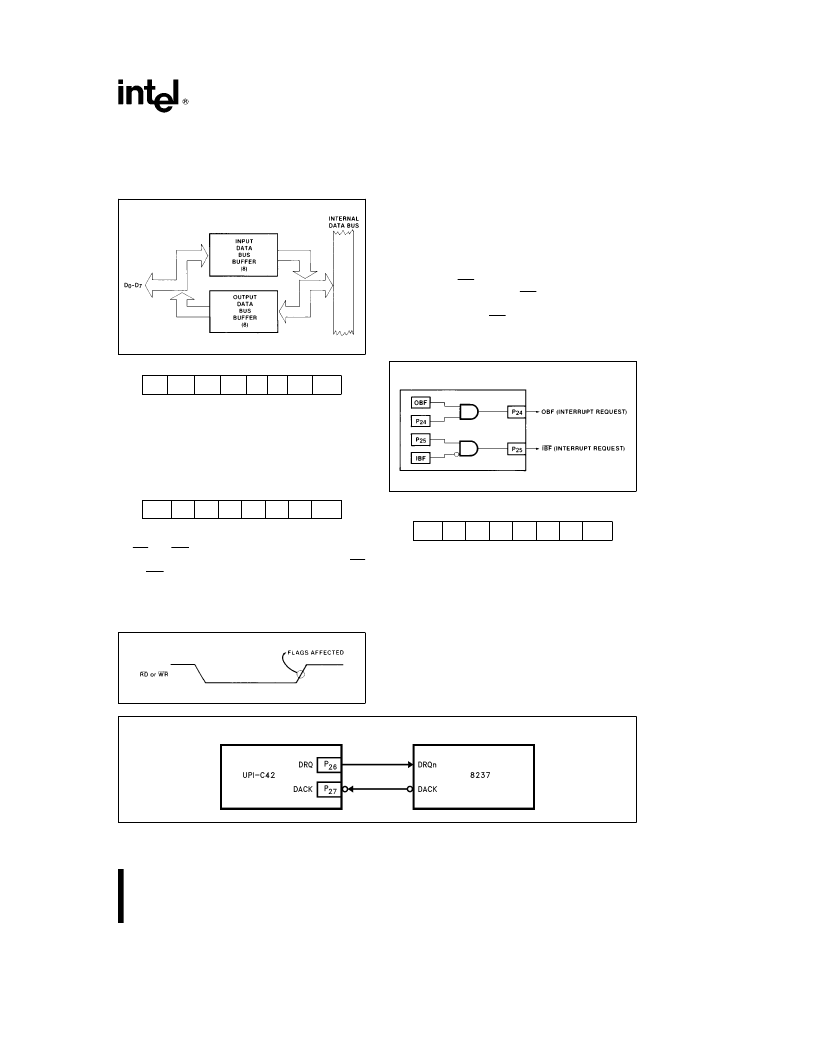

Two Data Bus Buffers, one for input and one for

output. This allows a much cleaner Master/Slave

protocol.

290414–5

2.

8 Bits of Status

ST

7

ST

6

ST

5

ST

4

F

1

F

0

IBF OBF

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

ST

4

–ST

7

are user definable status bits. These

bits are defined by the ‘‘MOV STS, A’’ single

byte, single cycle instruction. Bits 4–7 of the

acccumulator are moved to bits 4–7 of the status

register. Bits 0–3 of the status register are not

affected.

MOV STS, A

Op Code: 90H

1

0

0

1

0

0

0

0

D

7

D

0

3.

RD and WR are edge triggered. IBF, OBF, F

1

and

INT change internally after the trailing edge of RD

or WR.

During the time that the host CPU is reading the

status register, the UPI is prevented from updat-

ing this register or is ‘locked out.’

290414–6

4.

P

24

and P

25

are port pins or Buffer Flag pins

which can be used to interrupt a master proces-

sor. These pins default to port pins on Reset.

If the ‘‘EN FLAGS’’ instruction has been execut-

ed, P

24

becomes the OBF (Output Buffer Full)

pin. A ‘‘1’’ written to P

24

enables the OBF pin (the

pin outputs the OBF Status Bit). A ‘‘0’’ written to

P

24

disables the OBF pin (the pin remains low).

This pin can be used to indicate that valid data is

available from the UPI (in Output Data Bus Buff-

er).

If ‘‘EN FLAGS’’ has been executed, P

25

be-

comes the IBF (Input Buffer Full) pin. A ‘‘1’’ writ-

ten to P

25

enables the IBF pin (the pin outputs

the inverse of the IBF Status Bit. A ‘‘0’’ written to

P

25

disables the IBF pin (the pin remains low).

This pin can be used to indicate that the UPI is

ready for data.

Data Bus Buffer Interrupt Capability

290414–7

EN FLAGS

Op Code: 0F5H

1

1

1

1

0

1

0

1

D

7

D

0

5.

P

26

and P

27

are port pins or DMA handshake

pins for use with a DMA controller. These pins

default to port pins on Reset.

If the ‘‘EN DMA’’ instruction has been executed,

P

26

becomes the DRQ (DMA Request) pin. A ‘‘1’’

written to P

26

causes a DMA request (DRQ is

activated). DRQ is deactivated by DACK

#

RD,

DACK

#

WR, or execution of the ‘‘EN DMA’’ in-

struction.

DMA Handshake Capability

290414–8

5

相关PDF资料 |

PDF描述 |

|---|---|

| P82C435 | ENHANCED GRAPHICS CONTROLLER / BUS INTERFACE |

| P82C436 | ENHANCED GRAPHICS CONTROLLER / BUS INTERFACE |

| P82C550A | STARLAN SERIAL INTERFACE |

| P82C551 | STARLAN HUB CONTROLLER |

| P83C053BBPNB | MICROCONTROLLER FOR TELEVISION AND VIDEO (MTV) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| P87C453EBAA | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontrollers |

| P87C453EBL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| P87C453EBLKA | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontrollers |

| P87C453EFAA | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontrollers |

| P87C453EFL | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。