- 您现在的位置:买卖IC网 > PDF目录69042 > PC13892JVK (FREESCALE SEMICONDUCTOR INC) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA139 PDF资料下载

参数资料

| 型号: | PC13892JVK |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 电源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA139 |

| 封装: | 7 X 7 MM, 0.50 MM PITCH, ROHS COMPLIANT, PLASTIC, MO-195AD, BGA-139 |

| 文件页数: | 38/75页 |

| 文件大小: | 3848K |

| 代理商: | PC13892JVK |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

Analog Integrated Circuit Device Data

Freescale Semiconductor

43

13892

FUNCTIONAL DESCRIPTION

FUNCTIONAL PIN DESCRIPTION

Because of an order from the United States International Trade Commission, BGA-packaged product lines and part numbers indicated here currently are not

available from Freescale for import or sale in the United States prior to September 2010: MC13892VK and MC13892VL in 139, 186 MAPBGA packages.

WDI

Watchdog input. This pin must be high to stay in the On

mode. The WDI IO supply voltage is referenced to SPIVCC

(normally connected to SW4=1.8 V). SPIVCC must therefore

remain enabled to allow for proper WDI detection. If WDI

goes low, the system will transition to the Off state or Cold

Start (depending on the configuration).

STANDBY AND STANDBYSEC

Standby input signal from processor and from peripherals

respectively.

To ensure that shared resources are properly powered

when required, the system will only be allowed into Standby

when both the application processor (which typically controls

the STANDBY pin) and peripherals (which typically control

the STANDBYSEC pin) allow it. This is referred to as a

Standby event.

The Standby pins are programmable for Active High or

Active Low polarity, and that decoding of a Standby event will

take into account the programmed input polarities associated

with each pin. Since the Standby pin activity is driven

asynchronously to the system, a finite time is required for the

internal logic to qualify and respond to the pin level changes.

The state of the Standby pins only have influence in the On

mode and are therefore ignored during start up and in the

Watchdog phase. This allows the system to power up without

concern of the required Standby polarities, since software

can make adjustments accordingly, as soon as it is running.

INT

Interrupt to processor. Unmasked interrupt events are

signaled to the processor by driving the INT pin high.

PWRON1, 2 AND 3

A turn on event can be accomplished by connecting an

open drain NMOS driver to the PWRONx pin of the 13892, so

that it is in effect a parallel path for the power key.

PUMS1 AND PUMS2

Power up mode supply setting. Default start-up of the

device is selectable by hardwiring the Power Up Mode Select

pins. The Power Up Mode Select pins (PUMS1 and PUMS2)

are used to configure the start-up characteristics of the

regulators. Supply enabling and output level options are

selected by hardworking the PUMS pins for the desired

configuration.

The following power up defaults table shows the initial

setup for the voltage level of the switchers and regulators,

and if they get enabled or not, according to the PUMS pins

configuration.

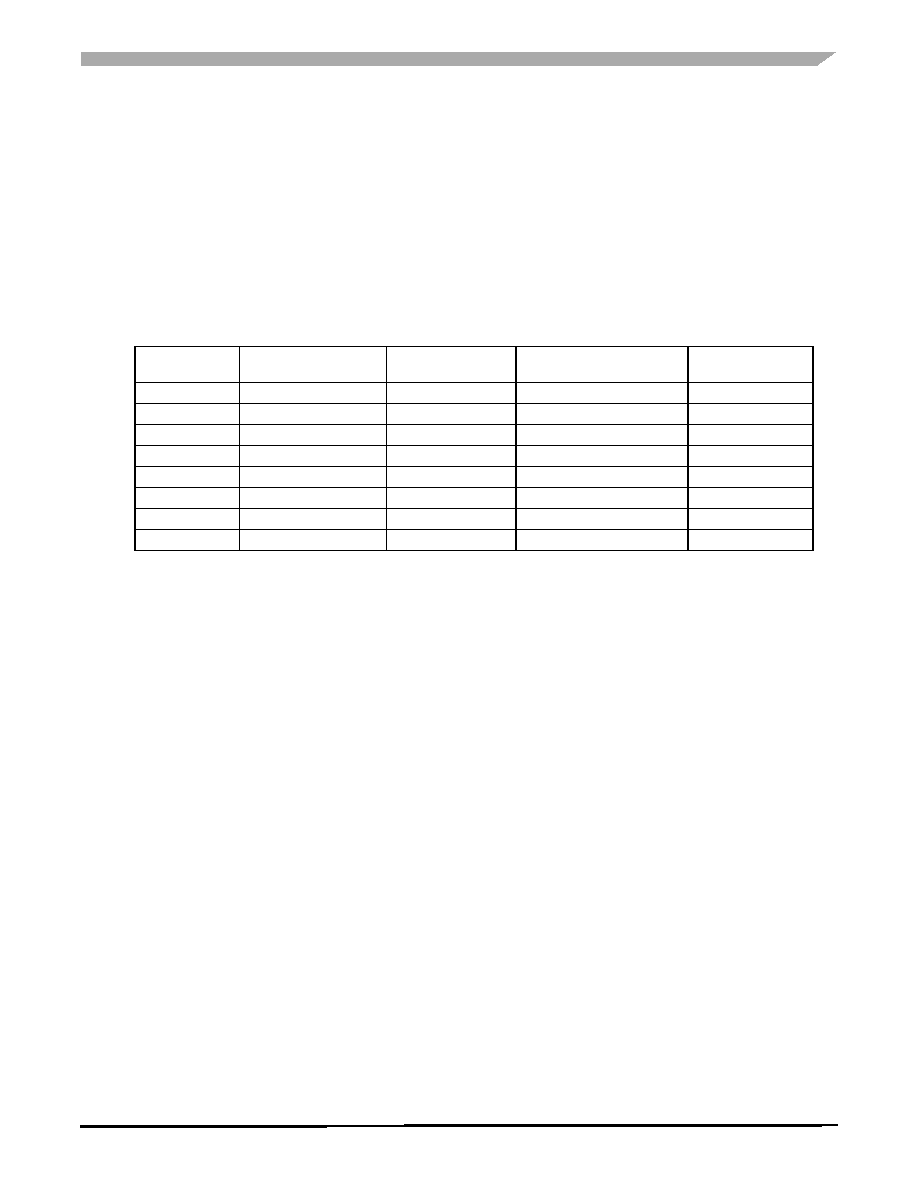

Table 8. Standby Control Pins

STANDBY (PIN)

STANDBYINV (SPI BIT)

STANDBYSEC (PIN)

STANDBYSECINV (SPI BIT)

STANDBY

CONTROL(42)

0

x

0

x

0

1

x

0

x

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Notes

42.

STANDBY = 0: System is not in Standby; STANDBY=1: System is in Standby and Standby programmability is activated.

相关PDF资料 |

PDF描述 |

|---|---|

| PC14568ED | SPECIALTY ANALOG CIRCUIT, PDIP16 |

| PC14568P | SPECIALTY ANALOG CIRCUIT, PDIP16 |

| PC14568EDR2 | SPECIALTY ANALOG CIRCUIT, PDIP16 |

| PC33880DWB | BRUSH DC MOTOR CONTROLLER, 2 A, PDSO28 |

| PC33880DW | BRUSH DC MOTOR CONTROLLER, 2 A, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PC13892JVK/R2 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Power Management and User Interface IC |

| PC13892JVKR2 | 制造商:Freescale Semiconductor 功能描述:POWER MGMT IC - Tape and Reel |

| PC13892JVL | 制造商:Freescale Semiconductor 功能描述: 制造商:Freescale Semiconductor 功能描述:5/28V BCK/BST PMUIC - Trays |

| PC13892JVL/R2 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Power Management and User Interface IC |

| PC13892JVLR2 | 制造商:Freescale Semiconductor 功能描述:5/28V BCK/BST PMUIC - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。