- 您现在的位置:买卖IC网 > PDF目录367933 > PH28F128L18B85 (INTEL CORP) StrataFlash Wireless Memory PDF资料下载

参数资料

| 型号: | PH28F128L18B85 |

| 厂商: | INTEL CORP |

| 元件分类: | PROM |

| 英文描述: | StrataFlash Wireless Memory |

| 中文描述: | 8M X 16 FLASH 1.8V PROM, 85 ns, PBGA56 |

| 封装: | 0.75 MM PITCH, LEAD FREE, VFBGA-56 |

| 文件页数: | 19/106页 |

| 文件大小: | 1272K |

| 代理商: | PH28F128L18B85 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

Intel StrataFlash Wireless Memory (L18)

Datasheet

Intel StrataFlash Wireless Memory (L18)

Order Number: 251902, Revision: 009

April 2005

19

4.2

Signal Descriptions

This section includes signal descriptions for the following packages:

VF BGA Package Signal Descriptions

SCSP Package Signal Descriptions

4.2.1

VF BGA Package Signal Descriptions

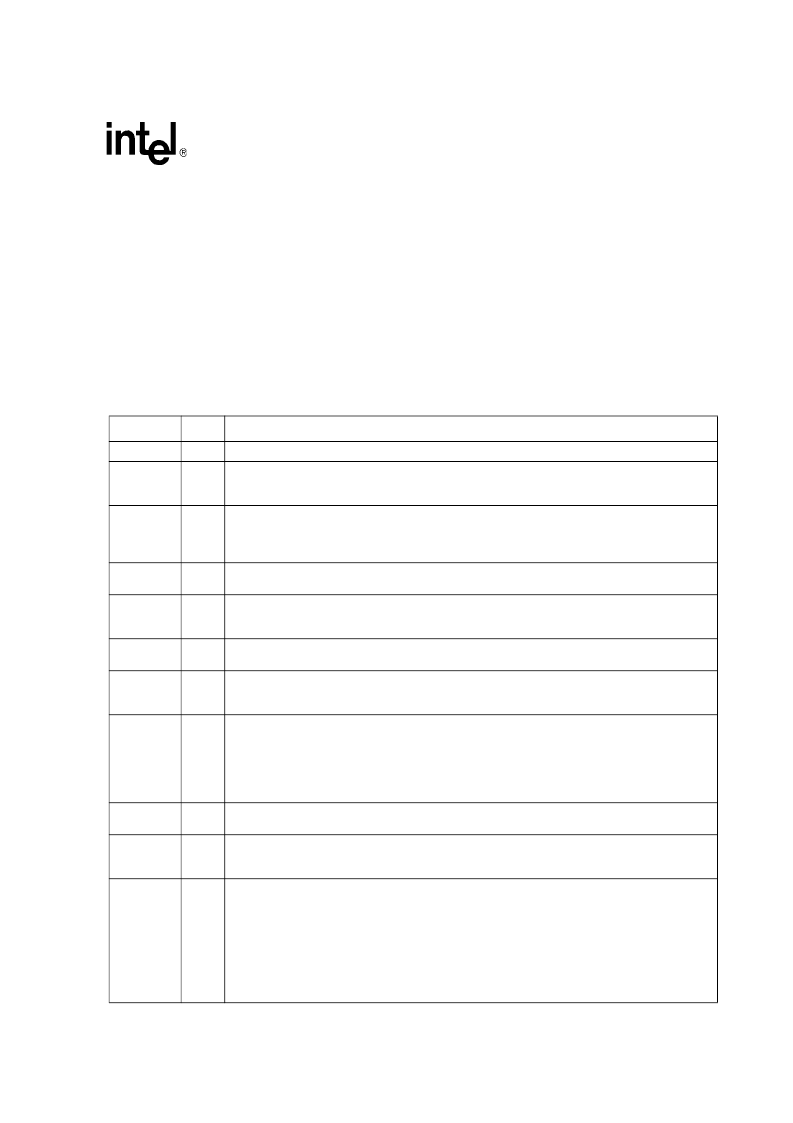

Table 1

describes the active signals used on the Intel StrataFlash Wireless Memory (L18), VF

BGA package.

Table 1.

Signal Descriptions (Sheet 1 of 2)

Symbol

Type

Name and Function

A[MAX:0]

Input

ADDRESS:

Device address inputs. 64-Mbit: A[21:0]; 128-Mbit: A[22:0]; 256-Mbit: A[23:0].

DQ[15:0]

Input/

Output

DATA INPUT/OUTPUTS:

Inputs data and commands during write cycles; outputs data during memory,

Status Register, Protection Register, and Read Configuration Register reads. Data balls float when the

CE# or OE# are deasserted. Data is internally latched during writes.

ADV#

Input

ADDRESS VALID:

Active-low input. During synchronous read operations, addresses are latched on

the rising edge of ADV#, or on the next valid CLK edge with ADV# low, whichever occurs first.

In asynchronous mode, the address is latched when ADV# going high or continuously flows through if

ADV# is held low.

CE#

Input

CHIP ENABLE:

Active-low input. CE#-low selects the device. CE#-high deselects the device, placing it

in standby, with DQ[15:0] and WAIT in High-Z.

CLK

Input

CLOCK:

Synchronizes the device with the system’s bus frequency in synchronous-read mode and

increments the internal address generator. During synchronous read operations, addresses are latched

on the rising edge of ADV#, or on the next valid CLK edge with ADV# low, whichever occurs first.

OE#

Input

OUTPUT ENABLE:

Active-low input. OE#-low enables the device’s output data buffers during read

cycles. OE#-high places the data outputs in High-Z and WAIT in High-Z.

RST#

Input

RESET:

Active-low input. RST# resets internal automation and inhibits write operations. This provides

data protection during power transitions. RST#-high enables normal operation. Exit from reset places

the device in asynchronous read array mode.

WAIT

Output

WAIT:

Indicates data valid in synchronous array or non-array burst reads. Configuration Register bit 10

(RCR[10], WT) determines its polarity when asserted. With CE# and OE# at V

, WAIT’s active output

is V

OL

or V

OH

when CE# and OE# are asserted. WAIT is high-Z if CE# or OE# is V

IH

.

In synchronous array or non-array read modes, WAIT indicates invalid data when asserted and

valid data when deasserted.

In asynchronous page mode, and all write modes, WAIT is deasserted.

WE#

Input

WRITE ENABLE:

Active-low input. WE# controls writes to the device. Address and data are latched on

the rising edge of WE#.

WP#

Input

WRITE PROTECT:

Active-low input. WP#-low enables the lock-down mechanism. Blocks in lock-down

cannot be unlocked with the Unlock command. WP#-high overrides the lock-down function enabling

blocks to be erased or programmed using software commands.

VPP

Power

/lnput

Erase and Program Power:

A valid voltage on this pin allows erasing or programming. Memory

contents cannot be altered when V

PP

≤

V

PPLK

. Block erase and program at invalid V

PP

voltages should

not be attempted.

Set V

= V

for in-system program and erase operations. To accommodate resistor or diode drops

from the system supply, the V

level of V

can be as low as V

min. V

must remain above

V

PPL

min to perform in-system program or erase. VPP may be 0 V during read operations.

V

can be applied to main blocks for 1000 cycles maximum and to parameter blocks for 2500 cycles.

VPP can be connected to 9 V for a cumulative total not to exceed 80 hours. Extended use of this pin at

9 V may derate flash performance/behavior.

相关PDF资料 |

PDF描述 |

|---|---|

| PH28F128L18T85 | StrataFlash Wireless Memory |

| PH28F256L18B85 | StrataFlash Wireless Memory |

| PH28F256L18T85 | StrataFlash Wireless Memory |

| PH28F640L18B85 | StrataFlash Wireless Memory |

| PH28F640L18T85 | StrataFlash Wireless Memory |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PH28F128L18B85A | 制造商:Micron Technology Inc 功能描述:128MB, TYAX .75 VFBGA 1.8 LF - Trays |

| PH28F128L18T85 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:StrataFlash Wireless Memory |

| PH28F128W18BD60A | 制造商:Micron Technology Inc 功能描述:NOR Flash Parallel 1.8V 128Mbit 8M x 16bit 60ns 56-Pin VFBGA Tray |

| PH28F160C3BD70A | 制造商:Micron Technology Inc 功能描述:MM#865392FLASH 28F160C3BD 70 VF-PBGA46 C |

| PH28F256L18B85 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:StrataFlash Wireless Memory |

发布紧急采购,3分钟左右您将得到回复。