- 您现在的位置:买卖IC网 > PDF目录376275 > PSD834F4V-70 (意法半导体) Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V PDF资料下载

参数资料

| 型号: | PSD834F4V-70 |

| 厂商: | 意法半导体 |

| 英文描述: | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| 中文描述: | Flash在系统可编程(ISP)的周边8位MCU,5V的 |

| 文件页数: | 37/110页 |

| 文件大小: | 1737K |

| 代理商: | PSD834F4V-70 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页

37/110

PSD813F2, PSD833F2, PSD834F2, PSD853F2, PSD854F2

Output Macrocell (OMC)

Eight of the Output Macrocells (OMC) are con-

nected to Ports A and B pins and are named as

McellAB0-McellAB7. The other eight macrocells

are connected to Ports B and C pins and are

named as McellBC0-McellBC7. If an McellAB out-

put is not assigned to a specific pin in PSDabel,

the Macrocell Allocator block assigns it to either

Port A or B. The same is true for a McellBC output

on Port B or C. Table

15

shows the macrocells and

port assignment.

The Output Macrocell (OMC) architecture is

shown in

Figure 16., page 39

. As shown in the fig-

ure, there are native product terms available from

the AND Array, and borrowed product terms avail-

able (if unused) from other Output Macrocells

(OMC). The polarity of the product term is con-

trolled by the XOR gate. The Output Macrocell

(OMC) can implement either sequential logic, us-

ing the flip-flop element, or combinatorial logic.

The multiplexer selects between the sequential or

combinatorial logic outputs. The multiplexer output

can drive a port pin and has a feedback path to the

AND Array inputs.

The flip-flop in the Output Macrocell (OMC) block

can be configured as a D, T, JK, or SR type in the

PSDabel program. The flip-flop’s clock, preset,

and clear inputs may be driven from a product

term of the AND Array. Alternatively, CLKIN (PD1)

can be used for the clock input to the flip-flop. The

flip-flop is clocked on the rising edge of CLKIN

(PD1). The preset and clear are active High inputs.

Each clear input can use up to two product terms.

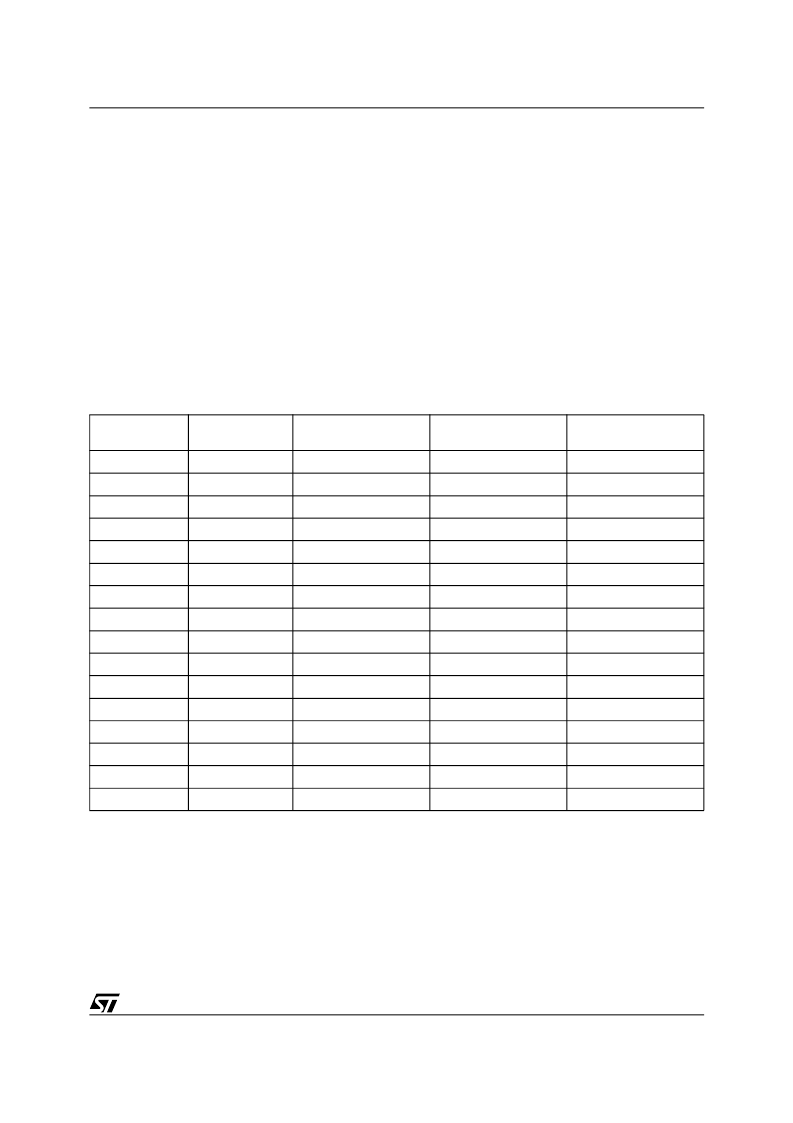

Table 15. Output Macrocell Port and Data Bit Assignments

Output

Macrocell

Port

Assignment

Native Product Terms

Maximum Borrowed

Product Terms

Data Bit for Loading or

Reading

McellAB0

Port A0, B0

3

6

D0

McellAB1

Port A1, B1

3

6

D1

McellAB2

Port A2, B2

3

6

D2

McellAB3

Port A3, B3

3

6

D3

McellAB4

Port A4, B4

3

6

D4

McellAB5

Port A5, B5

3

6

D5

McellAB6

Port A6, B6

3

6

D6

McellAB7

Port A7, B7

3

6

D7

McellBC0

Port B0, C0

4

5

D0

McellBC1

Port B1, C1

4

5

D1

McellBC2

Port B2, C2

4

5

D2

McellBC3

Port B3, C3

4

5

D3

McellBC4

Port B4, C4

4

6

D4

McellBC5

Port B5, C5

4

6

D5

McellBC6

Port B6, C6

4

6

D6

McellBC7

Port B7, C7

4

6

D7

相关PDF资料 |

PDF描述 |

|---|---|

| PSD854F4V-70 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD814F4V-90 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD834F5V-20 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD854F5V-20 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD814F5V-70 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PSD835G2-70U | 功能描述:静态随机存取存储器 5.0V 4M 70ns RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| PSD835G2-90U | 功能描述:静态随机存取存储器 5.0V 4M 90ns RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| PSD835G2-90UI | 功能描述:静态随机存取存储器 5.0V 4M 90ns RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| PSD835G2V-12UI | 功能描述:静态随机存取存储器 3.0V 4M 120ns RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| PSD835G2V-90U | 功能描述:静态随机存取存储器 3.0V 4M 90ns RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。