- 您现在的位置:买卖IC网 > PDF目录134952 > QS5917T-100TJ (INTEGRATED DEVICE TECHNOLOGY INC) 5917 SERIES, PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PQCC28 PDF资料下载

参数资料

| 型号: | QS5917T-100TJ |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | Clock Driver |

| 英文描述: | 5917 SERIES, PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PQCC28 |

| 封装: | PLASTIC, LCC-28 |

| 文件页数: | 5/7页 |

| 文件大小: | 75K |

| 代理商: | QS5917T-100TJ |

INDUSTRIALTEMPERATURERANGE

QS5917T

LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER

5

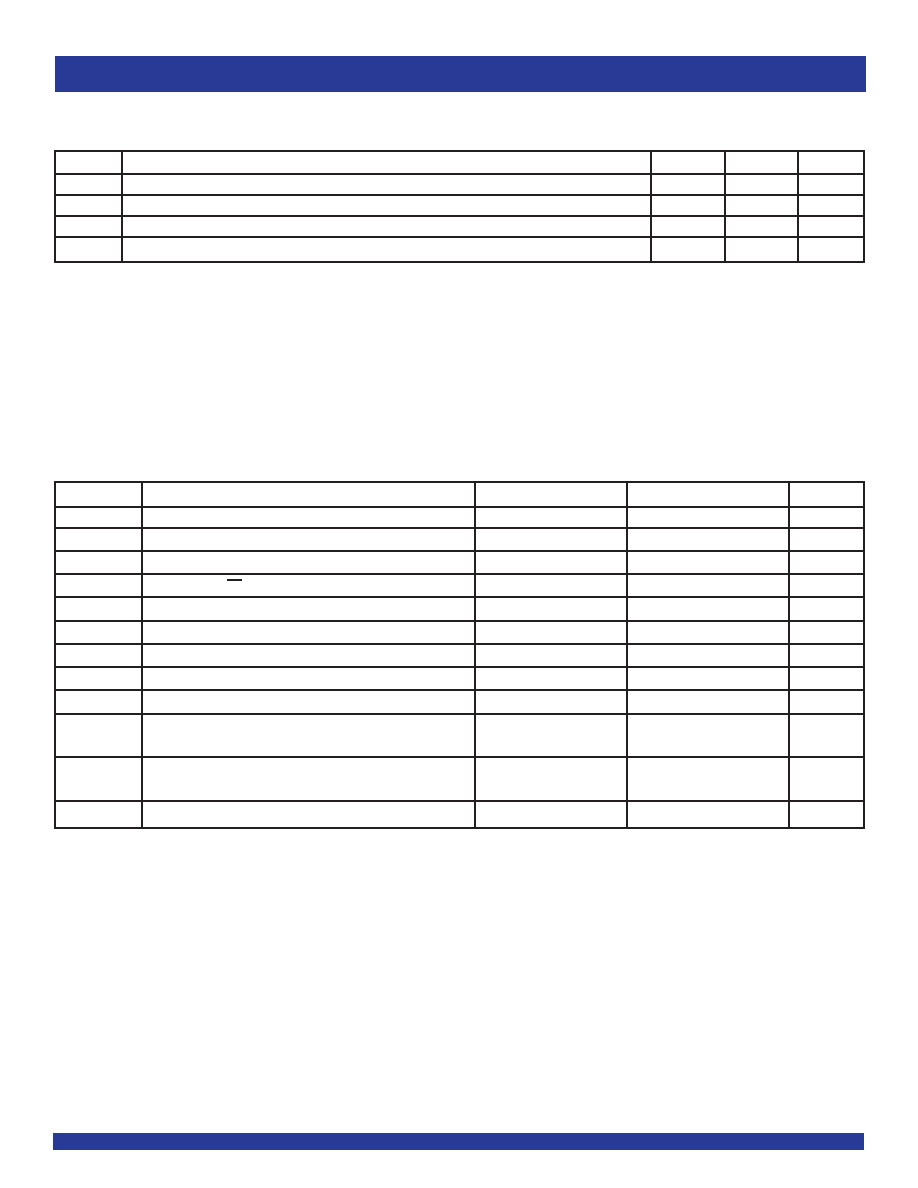

INPUT TIMING REQUIREMENTS

Symbol

Description

Min.

Max.

Unit

tR, tF

Maximum input rise and fall times, 0.8V to 2V

—

3

ns

FI

Input Clock Frequency, SYNC0, SYNC1 (1)

14

F2XQ

MHz

tPWC

Input clock pulse, HIGH or LOW

2

—

ns

DH

Duty cycle, SYNC0, SYNC1

25

75

%

NOTE:

1. The FI specification is based on Q output feedback. See the Frequency Selection Table for more detail on allowable SYNC input frequencies for different feedback combinations.

SWITCHING CHARACTERISTICS(1)

Symbol

Parameter

Min.

Max.

Unit

tSKR

Output Skew Between Rising Edges, Q0-Q4 and Q/2 (1)

—

350

ps

tSKF

Output Skew Between Falling Edges, Q0-Q4 (1)

—

350

ps

tSKALL

Output Skew, All Outputs (1)

—

500

ps

tPW

Pulse Width, Q5, 2xQ outputs

TCY/2

0.65

TCY/2 + 0.65

ns

tPW

Pulse Width, Q0-Q4, Q/2outputs (1)

TCY/2

0.5

TCY/2 + 0.5

ns

tJ

Cycle-to-Cycle Jitter, 33MHz (3)

—

0.25

ns

tPD

SYNC Input to Feedback Delay, 28MHz

100

400

ps

tPD

SYNC Input to Feedback Delay, 33MHz, 50

Ω to 1.5V

100

400

ps

tLOCK

SYNC to Phase Lock

—

10

ms

tPZH

Output Enable Time, RST LOW to HIGH (2)

07

ns

tPZL

tPHZ

Output Disable Time, RST HIGH to LOW (2)

06

ns

tPLZ

tR,tF

Output Rise/Fall Times, 0.8V to 2V

0.4

1.5

ns

NOTES:

1. Skew specifications apply under identical environments (loading, temperature, VDD, device speed grade).

2. Measured in open loop mode PLL_EN = 0.

3. Jitter is characterized using an oscilloscope. Measurement is taken one cycle after jitter. Jitter is characterized but not tested. See FREQUENCY SELECTION TABLE for information

on proper FREQ_SEL level for specified input frequencies.

相关PDF资料 |

PDF描述 |

|---|---|

| QS3251S1 | F/FAST SERIES, 1 LINE TO 8 LINE MULTIPLEXER AND DEMUX/DECODER, TRUE OUTPUT, PDSO16 |

| QS3384Q | 3384 SERIES, 10-BIT DRIVER, TRUE OUTPUT, PDSO24 |

| RSB6RM29160911 | 20 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| RSB6RM29200112 | 20 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

| RSB6RM29200313 | 20 A, BARRIER STRIP TERMINAL BLOCK, 1 ROW, 1 DECK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QS5917T-100TJ8 | 制造商:Integrated Device Technology Inc 功能描述:CLK DRVR PLL, FILTER PLCC28 - Tape and Reel |

| QS5917T-100TJG | 制造商:Integrated Device Technology Inc 功能描述:PLL CLOCK DRVR SGL 28PLCC - Rail/Tube |

| QS5917T-100TJG8 | 制造商:Integrated Device Technology Inc 功能描述:CLK DRVR PLL, FILTER. PLCC28 - Tape and Reel |

| QS5917T100TQ | 制造商:Integrated Device Technology Inc 功能描述: |

| QS5917T-100TQ | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:LOW SKEW CMOS PLL CLOCK DRIVER WITH INTEGRATED LOOP FILTER |

发布紧急采购,3分钟左右您将得到回复。