- 您现在的位置:买卖IC网 > PDF目录225036 > RG82845MZ Controller Miscellaneous - Datasheet Reference PDF资料下载

参数资料

| 型号: | RG82845MZ |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器杂项-数据表参考 |

| 文件页数: | 15/157页 |

| 文件大小: | 1407K |

| 代理商: | RG82845MZ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页

Intel

82845MP/82845MZ Chipset-Mobile (MCH-M)

250687-002

Datasheet

111

R

4.3.

System Management Mode (SMM) Memory Range

The MCH-M supports the use of main memory as System Management RAM (SMRAM) enabling the

use of System Management Mode. The MCH-M supports three SMRAM options: Compatible SMRAM

(C_SMRAM), High Segment (HSEG), and Top of Memory Segment (TSEG). System Management

RAM (SMRAM) space provides a memory area that is available for the SMI handler’s and code and data

storage. This memory resource is normally hidden from the system OS so that the processor has

immediate access to this memory space upon entry to SMM. MCH-M provides three SMRAM options:

Below 1 MByte option that supports compatible SMI handlers.

Above 1 MByte option that allows new SMI handlers to execute with write-back cacheable

SMRAM.

Optional larger write-back cacheable T_SEG area from 128 KB to 1MB in size above 1 MByte that

is reserved from the highest area in system DRAM memory. The above 1 MByte solutions require

changes to compatible SMRAM handlers’ code to properly execute above 1 MByte.

Note: Masters from the hub interface and AGP are not allowed to access the SMM space.

4.3.1.

SMM Space Definition

The addressed SMM space and the DRAM SMM space define SMM space. The addressed SMM space

is defined as the range of bus addresses used by the processor to access SMM space. DRAM SMM space

is defined as the range of physical DRAM memory locations containing the SMM code. SMM space can

be accessed at one of three transaction address ranges: Compatible, High and TSEG. The Compatible

and TSEG SMM space is not remapped and therefore the addressed and DRAM SMM space is the same

address range. Since the High SMM space is remapped the addressed and DRAM SMM space is a

different address range. Note that the High DRAM space is the same as the Compatible Transaction

Address space. Therefore the table below describes three unique address ranges:

Compatible Transaction Address (Adr C)

High Transaction Address (Adr H)

TSEG Transaction Address (Adr T)

These abbreviations are used later in the table describing SMM Space Transaction Handling.

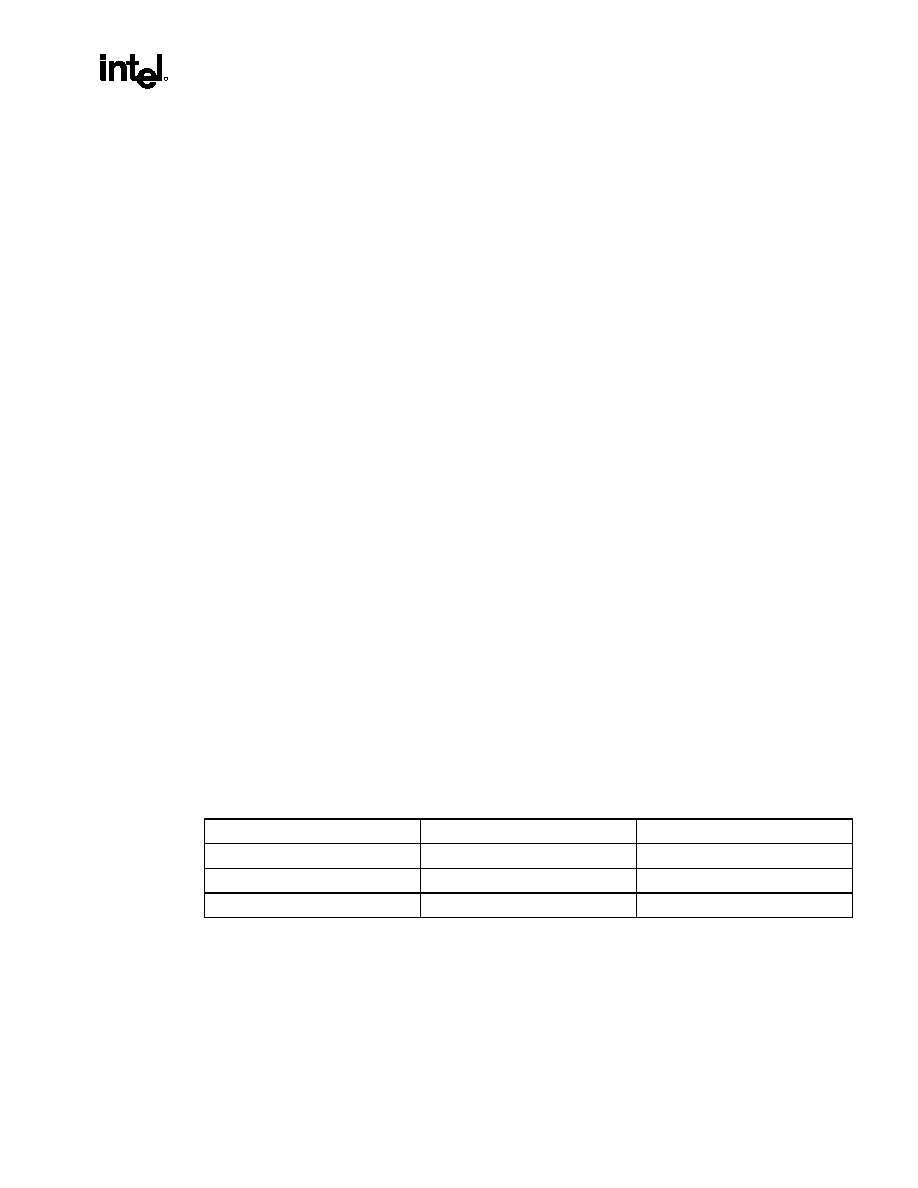

Table 26. SMM Space

SMM Space Enabled

Transaction Address Space (Adr)

DRAM Space (DRAM)

Compatible

A0000h to BFFFFh

High (H)

0FEDA0000h to 0FEDBFFFFh

A0000h to BFFFFh

TSEG (T)

(TOM-TSEG_SZ) to TOM

Note: High SMM: Note that this is different than in previous chipsets. In previous chipsets the High segment

was the 384-KB region from A0000h to FFFFFh. However, C0000h to FFFFFh was not practically

useful so it is deleted in MCH-M.

TSEG SMM: Note that this is different than in previous chip sets. In previous chip sets the TSEG

address space was offset by 256 MB to allow for simpler decoding and the TSEG was remapped to just

under the TOM. In the MCH-M 256 MB do not offset the TSEG region and it is not remapped.

相关PDF资料 |

PDF描述 |

|---|---|

| RG82870P2 | Controller Miscellaneous - Datasheet Reference |

| RH5RE36AA-T1-FA | 3.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PSSO3 |

| RH5RE56AA-T1-FA | 5.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PSSO3 |

| RE5RE36AA-TZ-FC | 3.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PBCY3 |

| RE5RE36AC-TZ-FC | 3.6 V FIXED POSITIVE LDO REGULATOR, 0.7 V DROPOUT, PBCY3 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RG82845PE S L6H5 | 制造商:Intel 功能描述:CHIPSTGMCH 82845PE HT-PBGA760 |

| RG82845PESL6Q3 | 制造商:Intel 功能描述:Chipsets |

| RG82845-SL5V7 | 制造商:Intel 功能描述:INTEL 845G GRAPHICS AND MEMORY CONTROLLER HUB(GMCH) |

| RG82845SL5YQ | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:Intel?? 845 Chipset: 82845 Memory Controller Hub (MCH) for SDR |

| RG82845-SL63W | 制造商:Intel 功能描述:INTEL 845G GRAPHICS AND MEMORY CONTROLLER HUB(GMCH) |

发布紧急采购,3分钟左右您将得到回复。