- 您现在的位置:买卖IC网 > PDF目录98071 > S80C186XL20 (INTEL CORP) 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 PDF资料下载

参数资料

| 型号: | S80C186XL20 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

| 封装: | EIAJ, QFP-80 |

| 文件页数: | 2/48页 |

| 文件大小: | 762K |

| 代理商: | S80C186XL20 |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

80C186XL80C188XL

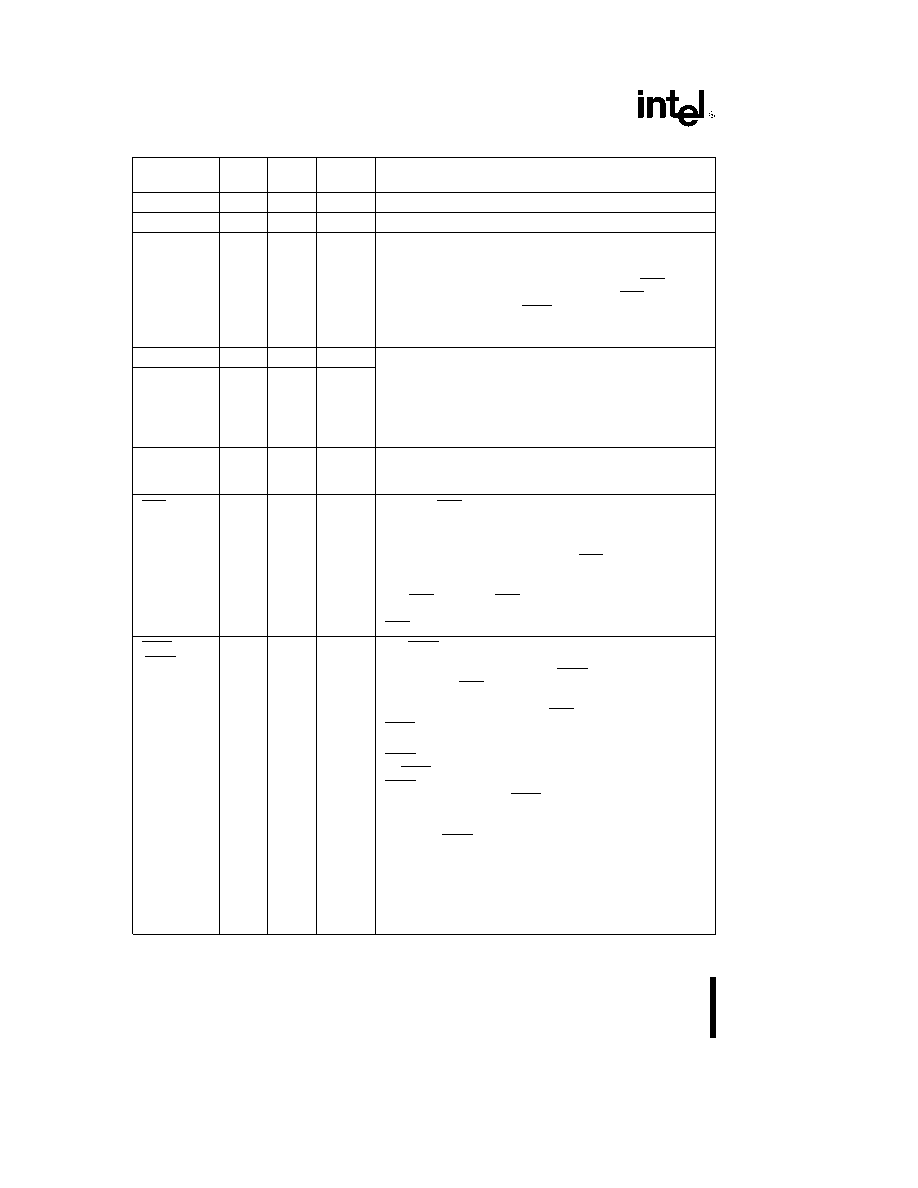

Table 3 Pin Descriptions

Pin

Input

Output

Pin Description

Name

Type

States

VCC

P

System Power a5 volt power supply

VSS

G

System Ground

RESET

O

H(0)

RESET Output indicates that the CPU is being reset and can

be used as a system reset It is active HIGH synchronized

R(1)

with the processor clock and lasts an integer number of

clock periods corresponding to the length of the RES signal

Reset goes inactive 2 clockout periods after RES goes

inactive When tied to the TEST BUSY pin RESET forces

the processor into enhanced mode RESET is not floated

during bus hold

X1

I

A(E)

Crystal Inputs X1 and X2 provide external connections for a

fundamental mode or third overtone parallel resonant crystal

X2

O

H(Q)

for the internal oscillator X1 can connect to an external

R(Q)

clock instead of a crystal In this case minimize the

capacitance on X2 The input or oscillator frequency is

internally divided by two to generate the clock signal

(CLKOUT)

CLKOUT

O

H(Q)

Clock Output provides the system with a 50% duty cycle

waveform All device pin timings are specified relative to

R(Q)

CLKOUT CLKOUT is active during reset and bus hold

RES

I

A(L)

An active RES causes the processor to immediately

terminate its present activity clear the internal logic and

enter a dormant state This signal may be asynchronous to

the clock The processor begins fetching instructions

approximately 6

clock cycles after RES is returned HIGH

For proper initialization VCC must be within specifications

and the clock signal must be stable for more than 4 clocks

with RES held LOW RES is internally synchronized This

input is provided with a Schmitt-trigger to facilitate power-on

RES generation via an RC network

TEST BUSY

I

A(E)

The TEST pin is sampled during and after reset to determine

whether the processor is to enter Compatible or Enhanced

(TEST)

Mode Enhanced Mode requires TEST to be HIGH on the

rising edge of RES and LOW four CLKOUT cycles later Any

other combination will place the processor in Compatible

Mode During power-up active RES is required to configure

TEST BUSY as an input A weak internal pullup ensures a

HIGH state when the input is not externally driven

TEST

In Compatible Mode this pin is configured to operate

as TEST This pin is examined by the WAIT instruction If the

TEST input is HIGH when WAIT execution begins instruction

execution will suspend TEST will be resampled every five

clocks until it goes LOW at which time execution will

resume If interrupts are enabled while the processor is

waiting for TEST interrupts will be serviced

BUSY (80C186XL Only)In Enhanced Mode this pin is

configured to operate as BUSY The BUSY input is used to

notify the 80C186XL of Math Coprocessor activity Floating

point instructions executing in the 80C186XL sample the

BUSY pin to determine when the Math Coprocessor is ready

to accept a new command BUSY is active HIGH

NOTE

Pin names in parentheses apply to the 80C188XL

10

相关PDF资料 |

PDF描述 |

|---|---|

| S80C188XL20 | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

| S80C188XL12 | 16-BIT, 12 MHz, MICROPROCESSOR, PQFP80 |

| SB80C186XL25 | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| SB80C188XL25 | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| S80C188EB-8 | 8-BIT, 8 MHz, MICROPROCESSOR, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S80C186XL25 | 功能描述:IC MPU 16-BIT 5V 25MHZ 80-MQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:- 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| S80C188 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:CMOS High-Integration 16-Bit Microprocessors |

| S80C188-12 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:CMOS High-Integration 16-Bit Microprocessors |

| S80C188-16 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:CMOS High-Integration 16-Bit Microprocessors |

| S80C188-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。