- 您现在的位置:买卖IC网 > PDF目录98071 > S80C186XL20 (INTEL CORP) 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 PDF资料下载

参数资料

| 型号: | S80C186XL20 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

| 封装: | EIAJ, QFP-80 |

| 文件页数: | 3/48页 |

| 文件大小: | 762K |

| 代理商: | S80C186XL20 |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

80C186XL80C188XL

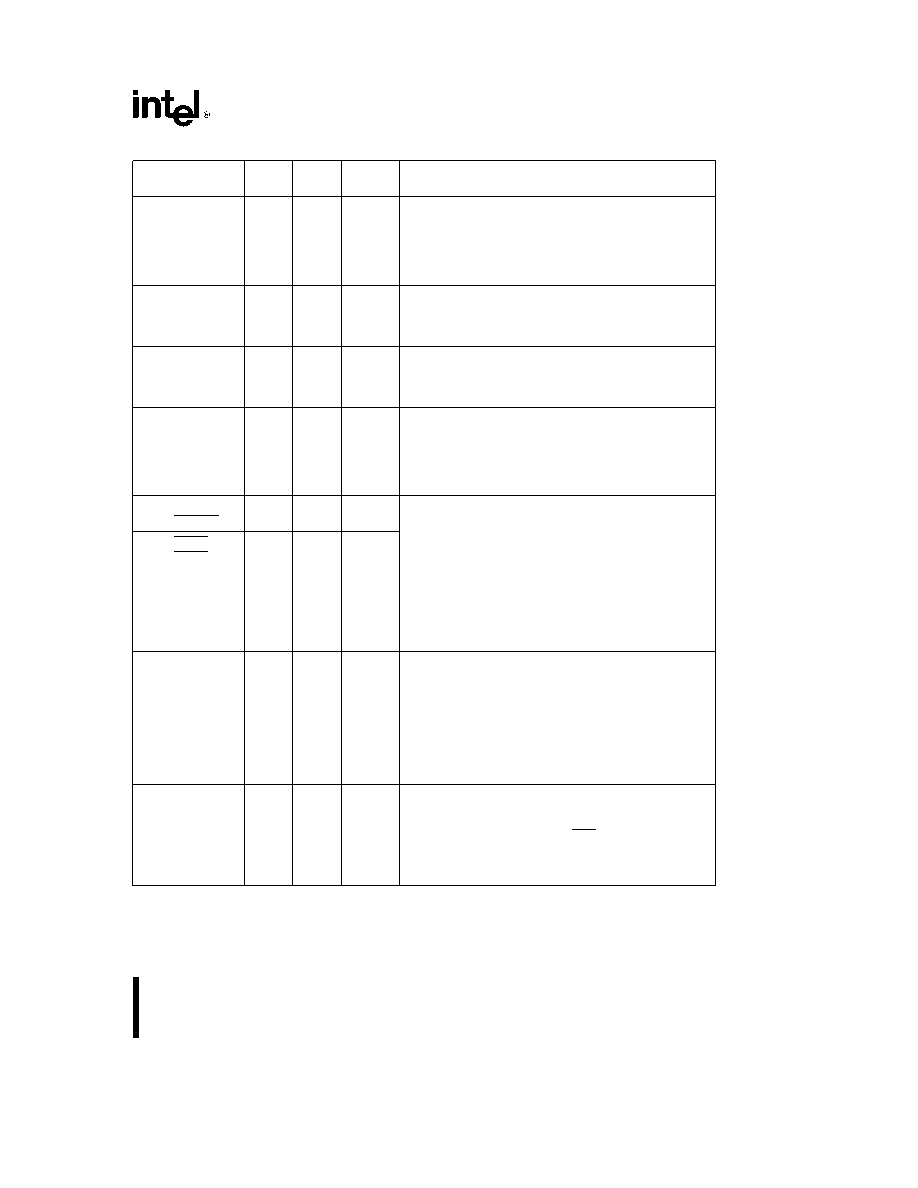

Table 3 Pin Descriptions

(Continued)

Pin

Input

Output

Pin Description

Name

Type

States

TMR IN 0

I

A(L)

Timer Inputs are used either as clock or control signals

depending upon the programmed timer mode These

TMR IN 1

A(E)

inputs are active HIGH (or LOW-to-HIGH transitions are

counted) and internally synchronized Timer Inputs must

be tied HIGH when not being used as clock or retrigger

inputs

TMR OUT 0

O

H(Q)

Timer outputs are used to provide single pulse or

continuous waveform generation depending upon the

TMR OUT 1

R(1)

timer mode selected These outputs are not floated

during a bus hold

DRQ0

I

A(L)

DMA Request is asserted HIGH by an external device

when it is ready for DMA Channel 0 or 1 to perform a

DRQ1

transfer These signals are level-triggered and internally

synchronized

NMI

I

A(E)

The Non-Maskable Interrupt input causes a Type 2

interrupt An NMI transition from LOW to HIGH is

latched and synchronized internally and initiates the

interrupt at the next instruction boundary NMI must be

asserted for at least one CLKOUT period The Non-

Maskable Interrupt cannot be avoided by programming

INT0

I

A(E)

Maskable Interrupt Requests can be requested by

activating one of these pins When configured as inputs

INT1SELECT

A(L)

these pins are active HIGH Interrupt Requests are

INT2INTA0

IO

A(E)

H(1)

synchronized internally INT2 and INT3 may be

INT3INTA1 IRQ

A(L)

R(Z)

configured to provide active-LOW interrupt-

acknowledge output signals All interrupt inputs may be

configured to be either edge- or level-triggered To

ensure recognition all interrupt requests must remain

active until the interrupt is acknowledged When Slave

Mode is selected the function of these pins changes

(see Interrupt Controller section of this data sheet)

A19S6

O

H(Z)

Address Bus Outputs and Bus Cycle Status (3 – 6)

indicate the four most significant address bits during T1

A18S5

R(Z)

These signals are active HIGH

A17S4

A16S3

During T2 T3 TW and T4 the S6 pin is LOW to indicate

a CPU-initiated bus cycle or HIGH to indicate a DMA-

(A8 – A15)

initiated or refresh bus cycle During the same T-states

S3 S4 and S5 are always LOW On the 80C188XL

A15 – A8 provide valid address information for the entire

bus cycle

AD0 – AD15

IO

S(L)

H(Z)

AddressData Bus signals constitute the time

multiplexed memory or IO address (T1) and data (T2

(AD0 – AD7)

R(Z)

T3 TW and T4) bus The bus is active HIGH For the

80C186XL A0 is analogous to BHE for the lower byte of

the data bus pins D7 through D0 It is LOW during T1

when a byte is to be transferred onto the lower portion

of the bus in memory or IO operations

NOTE

Pin names in parentheses apply to the 80C188XL

11

相关PDF资料 |

PDF描述 |

|---|---|

| S80C188XL20 | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

| S80C188XL12 | 16-BIT, 12 MHz, MICROPROCESSOR, PQFP80 |

| SB80C186XL25 | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| SB80C188XL25 | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| S80C188EB-8 | 8-BIT, 8 MHz, MICROPROCESSOR, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S80C186XL25 | 功能描述:IC MPU 16-BIT 5V 25MHZ 80-MQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:- 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| S80C188 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:CMOS High-Integration 16-Bit Microprocessors |

| S80C188-12 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:CMOS High-Integration 16-Bit Microprocessors |

| S80C188-16 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:CMOS High-Integration 16-Bit Microprocessors |

| S80C188-20 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。