- 您现在的位置:买卖IC网 > PDF目录21883 > SFCF4096H2BU4TO-I-MS-517-STD (Swissbit NA Inc)FLASH SLC UDMA/MDMA/PIO 4GB PDF资料下载

参数资料

| 型号: | SFCF4096H2BU4TO-I-MS-517-STD |

| 厂商: | Swissbit NA Inc |

| 文件页数: | 24/102页 |

| 文件大小: | 0K |

| 描述: | FLASH SLC UDMA/MDMA/PIO 4GB |

| 标准包装: | 1 |

| 系列: | C-440 |

| 存储容量: | 4GB |

| 存储器类型: | CompactFlash? |

| 其它名称: | 1052-1093 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页

�� �

�

�

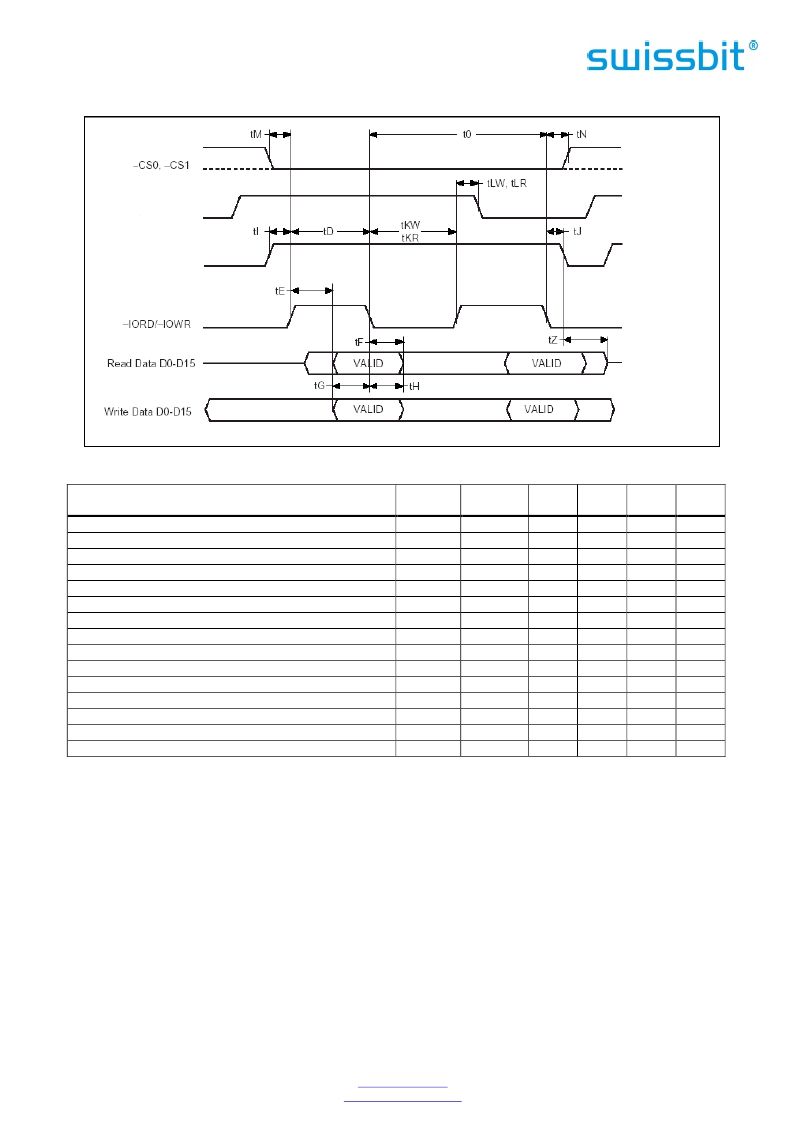

�Figure� 9:� True� IDE� Multi-Word� DMA� Mode� Read/Write� waveforms�

�–� DMARQ�

�–� DMACK�

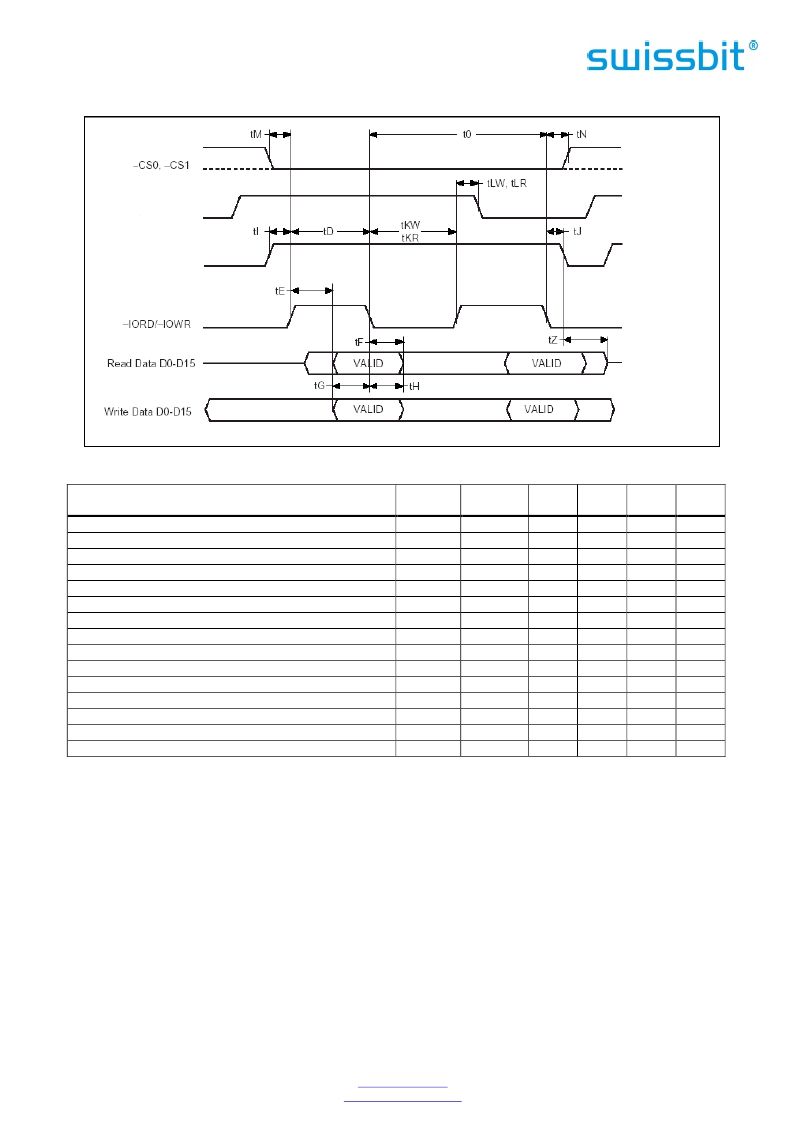

�Table� 24:� True� IDE� Multi-Word� DMA� Mode� Read/Write� timing�

�t� 0�

�t� D�

�t� KR�

�t� KW�

�Parameter�

�Cycle� time� (min)�

�-IORD� /� -IOWR� asserted� width� (min)�

�-IORD� data� access� (max)�

�-IORD� data� hold� (min)�

�-IORD/-IOWR� data� setup� (min)�

�-IOWR� data� hold� (min)�

�DMACK� to� –� IORD/-IOWR� setup� (min)�

�-IORD� /� -IOWR� to� –� DMACK� hold� (min)�

�-IORD� Low� width� (min)�

�-IOWR� Low� width� (min)�

�-IORD� to� DMARQ� delay� (max)�

�-IOWR� to� DMARQ� delay� (max)�

�CS(1:0)� valid� to� –� IORD� /� -IOWR� (min)�

�CS(1:0)� hold� (min)�

�Symbol�

�(1)�

�(1)�

�t� E�

�t� F�

�t� G�

�t� H�

�t� I�

�t� J�

�(1)�

�(1)�

�t� LR�

�t� LW�

�t� M�

�t� N�

�Mode� 0�

�(ns)�

�480�

�215�

�150�

�5�

�100�

�20�

�0�

�20�

�50�

�215�

�120�

�40�

�50�

�15�

�1�

�(ns)�

�150�

�80�

�60�

�5�

�30�

�15�

�0�

�5�

�50�

�50�

�40�

�40�

�30�

�10�

�2�

�(ns)�

�120�

�70�

�50�

�5�

�20�

�10�

�0�

�5�

�25�

�25�

�35�

�35�

�25�

�10�

�3�

�(ns)�

�100�

�65�

�50�

�5�

�15�

�5�

�0�

�5�

�25�

�25�

�35�

�35�

�10�

�10�

�4�

�(ns)�

�80�

�55�

�45�

�5�

�10�

�5�

�0�

�5�

�20�

�20�

�35�

�35�

�5�

�10�

�-DMACK� (max)� t� Z� 20� 25� 25� 25� 25�

�1.� t� 0� is� the� minimum� total� cycle� time.� T� D� is� the� minimum� command� active� time.� T� KR� and� t� KW� are� the� minimum� command� recovery� time�

�or� command� inactive� time� for� input� and� output� cycles,� respectively.� The� actual� cycle� time� is� the� sum� of� the� actual� command� active�

�time� and� the� actual� command� inactive� time.� The� timing� requirements� of� t� 0� ,� t� D� ,� t� KR� ,� and� t� KW� must� be� respected.� T� 0� is� higher� than� t� D� +�

�t� KR� or� t� D� +� t� KW� ,� for� input� and� output� cycles� respectively.� This� means� the� host� can� lengthen� either� t� D� or� t� KR� /t� KW� ,� or� both,� to� ensure�

�that� t� 0� is� equal� to� or� higher� than� the� value� reported� in� the� devices� identify� device� data.� A� CompactFlash� TM� Storage� Card�

�implementation� shall� support� any� legal� host� implementation.�

�6.5� Ultra� DMA� Mode�

�6.5.1� Ultra� DMA� Overview�

�Ultra� DMA� is� an� optional� data� transfer� protocol� used� with� the� READ� DMA,� and� WRITE� DMA,� commands.� When� this�

�protocol� is� enabled,� the� Ultra� DMA� protocol� shall� be� used� instead� of� the� Multiword� DMA� protocol� when� these�

�commands� are� issued� by� the� host.� This� protocol� applies� to� the� Ultra� DMA� data� burst� only.� When� this� protocol� is�

�used� there� are� no� changes� to� other� elements� of� the� ATA� protocol� (e.g.,� Command� Block� Register� access).�

�Ultra� DMA� operations� can� take� place� in� any� of� the� three� basic� interface� modes:� PC� Card� Memory� mode,� PC� Card� I/O�

�mode,� and� True� IDE� (the� original� mode� to� support� UDMA).� The� usage� of� signals� in� each� of� the� modes� is� shown� in�

��Swissbit� AG�

�Industriestrasse� 4�

�Swissbit� reserves� the� right� to� change� products� or� specifications� without� notice.�

�Revision:� 1.00�

�CH-9552� Bronschhofen�

�Switzerland�

�www.swissbit.com�

�industrial@swissbit.com�

�C-440_data_sheet_CF-HxBU_Rev100.doc�

�Page� 24� of� 102�

�相关PDF资料 |

PDF描述 |

|---|---|

| F3M-S1213 | SENSOR COMB 12" WAFER 13 SLOTS |

| MX3AWT-A1-0000-0007B8 | LED XLAMP WARM WHITE 350MA 2PLCC |

| MX3AWT-A1-0000-0007AA | LED XLAMP WARM WHITE 350MA 2PLCC |

| MX3SWT-A1-0000-0008B6 | LED XLAMP MX3S WHITE PLCC |

| MX3SWT-A1-0000-0008B5 | LED XLAMP MX3S WHITE PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SFCF4096H2BU4TO-I-MS-527-STD | 制造商:SWISSBIT NA INC 功能描述:FLASH |

| SFCF4096H4BK2SA-C-QT-553-SMA | 制造商:SWISSBIT NA INC 功能描述:FLASH |

| SFCF4096H4BK2SAIQT553SMA | 制造商:Swissbit 功能描述:Flash Card 4G-Byte 3.3V/5V CompactFlash |

| SFCF4096H4BK2SA-I-QT-553-SMA | 功能描述:FLASH SLC UDMA/MDMA/PIO 4G RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-300 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD? |

| SFCF64GBH2BU4TO-C-NU-527-STD | 制造商:SWISSBIT 功能描述:CFC C-440 DENSITY COMMERCIAL - Trays 制造商:SWISSBIT NA INC 功能描述:FLASH |

发布紧急采购,3分钟左右您将得到回复。