- 您现在的位置:买卖IC网 > PDF目录21883 > SFCF4096H2BU4TO-I-MS-517-STD (Swissbit NA Inc)FLASH SLC UDMA/MDMA/PIO 4GB PDF资料下载

参数资料

| 型号: | SFCF4096H2BU4TO-I-MS-517-STD |

| 厂商: | Swissbit NA Inc |

| 文件页数: | 30/102页 |

| 文件大小: | 0K |

| 描述: | FLASH SLC UDMA/MDMA/PIO 4GB |

| 标准包装: | 1 |

| 系列: | C-440 |

| 存储容量: | 4GB |

| 存储器类型: | CompactFlash? |

| 其它名称: | 1052-1093 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页

�� �

�

�

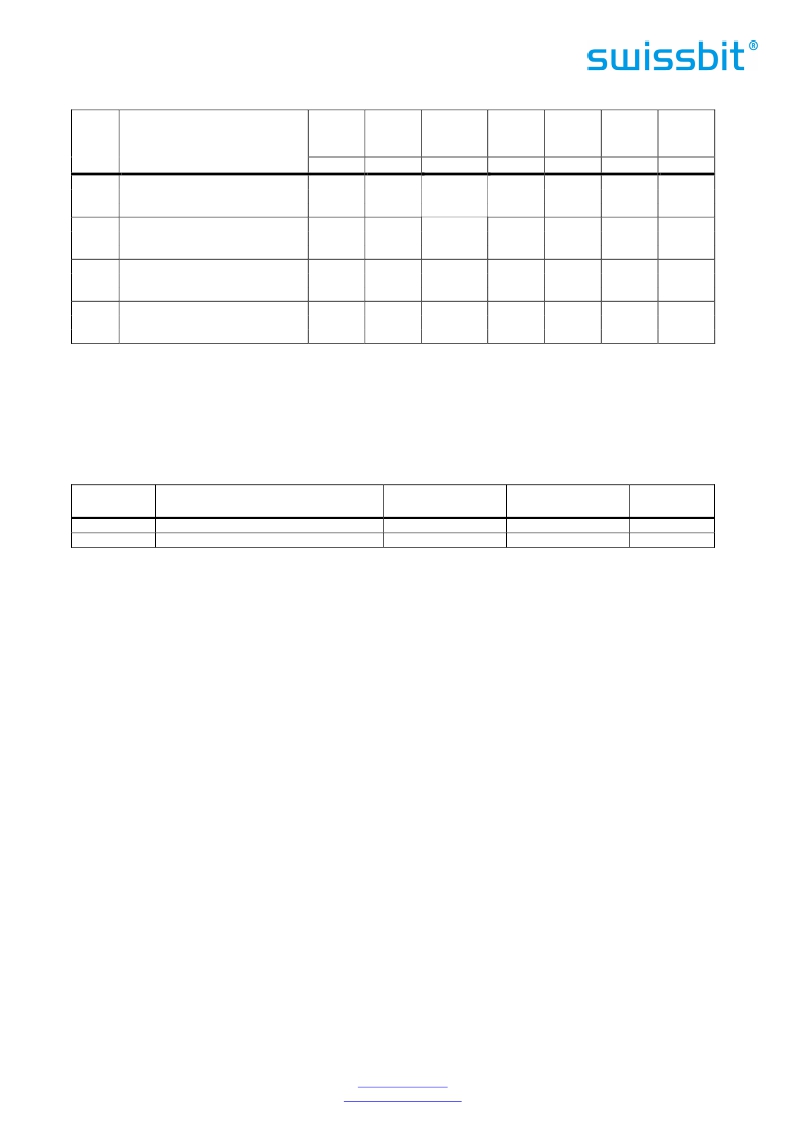

�Table� 28:� Ultra� DMA� Sender� and� Recipient� IC� Timing� Requirements�

�Name�

�Comments�

�UDMA�

�Mode� 0�

�(ns)�

�Min�

�UDMA�

�Mode� 1�

�(ns)�

�Min�

�UDMA�

�Mode� 2�

�(ns)�

�Min�

�UDMA�

�Mode� 3�

�(ns)�

�Min�

�UDMA�

�Mode4�

�(ns)�

�Min�

�UDMA�

�Mode� 5�

�(ns)�

�Min�

�UDMA�

�Mode6�

�(ns)�

�Min�

�t� DSIC�

�Recipient� IC� data� setup� time� (from�

�data� valid� until� STROBE� edge)�

�14.7�

�9.7�

�6.8�

�6.8�

�4.8�

�2.3�

�2.3�

�(see� note� 2)�

�t� DHIC�

�Recipient� IC� data� hold� time� (from�

�STROBE� edge� until� data� may�

�4.8�

�4.8�

�4.8�

�4.8�

�4.8�

�2.8�

�2.8�

�become� invalid)� (see� note� 2)�

�t� DVSIC�

�Sender� IC� data� valid� setup� time�

�(from� data� valid� until� STROBE�

�72.9�

�50.9�

�33.9�

�22.6�

�9.5�

�6.0�

�5.2�

�edge)� (see� note� 3)�

�t� DVHIC�

�Sender� IC� data� valid� hold� time�

�(from� STROBE� edge� until� data�

�9.0�

�9.0�

�9.0�

�9.0�

�9.0�

�6.0�

�5.2�

�may� become� invalid)� (see� note� 3)�

�Notes:�

�1.�

�2.�

�3.�

�All� timing� measurement� switching� points(low� to� high� and� high� to� low)� shall� be� taken� at� 1.5� V.�

�The� correct� data� value� shall� be� captured� by� the� recipient� given� input� data� with� a� slew� rate� of� 0.4� V/ns� rising� and� falling�

�and� the� input� STROBE� with� a� slew� rate� of� 0.4� V/ns� rising� and� falling� at� t� DSIC� and� t� DHIC� timing� (as� measured� through� 1.5�

�V).�

�The� parameters� t� DVSIC� and� t� DVHIC� shall� be� met� for� lumped� capacitive� loads� of� 15� and� 40� pF� at� the� IC� where� all� signals�

�have� the� same� capacitive� load� value.� Noise� that� may� couple� onto� the� output� signals� from� external� sources� has� not� been�

�included� in� these� values.�

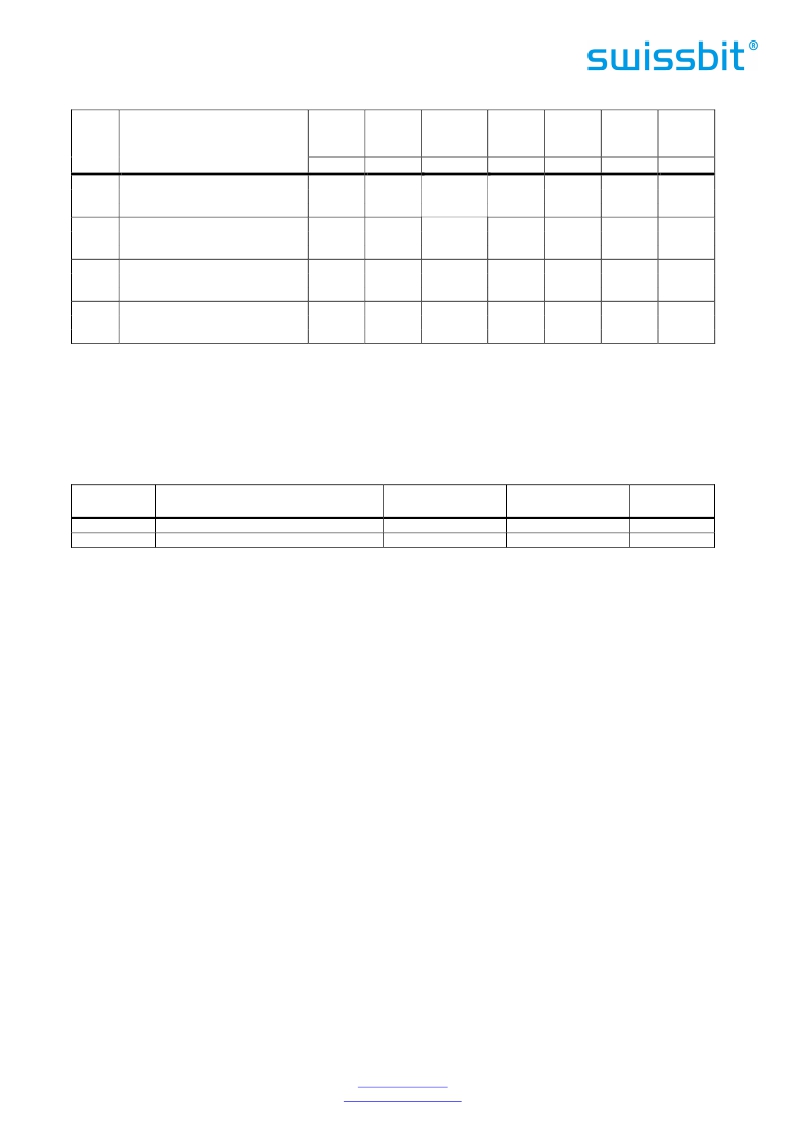

�Table 29: Ultr� a� DMA� AC� Signal� Requirements�

�Name�

�Comment�

�Min�

�Max�

�Notes�

�[V/ns]�

�[V/ns]�

�S� RISE�

�S� FALL�

�Rising� Edge� Slew� Rate� for� any� signal�

�Falling� Edge� Slew� Rate� for� any� signal�

�1.25�

�1.25�

�1�

�1�

�Note:�

�1.�

�The� sender� shall� be� tested� while� driving� an� 18� inch� long,� 80� conductor� cable� with� PVC� insulation� material.� The� signal�

�under� test� shall� be� cut� at� a� test� point� so� that� it� has� not� trace,� cable� or� recipient� loading� after� the� test� point.� All� other�

�signals� should� remain� connected� through� to� the� recipient.� The� test� point� may� be� located� at� any� point� between� the�

�sender’s� s� eries� termination� resistor� and� one� half� inch� or� less� of� conductor� exiting� the� connector.� If� the� test� point� is� on�

�a� cable� conductor� rather� than� the� PCB,� an� adjacent� ground� conductor� shall� also� be� cut� within� one� half� inch� of� the�

�connector.�

�The� test� load� and� test� points� should� then� be� soldered� directly� to� the� exposed� source� side� connectors.� The� test� loads�

�consist� of� a� 15� pF� or� a� 40� pF,� 5%,� 0.08� inch� by� 0.05� inch� surface� mount� or� smaller� size� capacitor� from� the� test� point� to�

�ground.� Slew� rates� shall� be� met� for� both� capacitor� values.�

�Measurements� shall� be� taken� at� the� test� point� using� a� <1� pF,� >100� kOhm,� 1� GHz� or� faster� probe� and� a� 500� MHz� or�

�faster� oscilloscope.� The� average� rate� shall� be� measured� from� 20%� to� 80%� of� the� settled� VOH� level� with� data�

�transitions� at� least� 120� ns� apart.� The� settled� VOH� level� shall� be� measured� as� the� average� output� high� level� under� the�

�defined� testing� conditions� from� 100� nsec� after� 80%� of� a� rising� edge� until� 20%� of� the� subsequent� falling� edge.�

�6.5.4.4.1� Initiating� an� Ultra� DMA� Data-In� Burst�

�a)� An� Ultra� DMA� Data-In� burst� is� initiated� by� following� the� steps� lettered� below.� The� timing� diagram� is�

�shown� in� Figure� 10:� Ultra� DMA� Data-In� Burst� Initiation� Timing.� The� associated� timing� parameters� are�

�specified� in� Table� 26:� Ultra� DMA� Data� Burst� Timing� Requirements� and� are� described� in� Table� 27:� Ultra� DMA�

��b)� The� following� steps� shall� occur� in� the� order� they� are� listed� unless� otherwise� specifically� allowed:�

�c)�

�The� host� shall� keep� –� DMACK� in� the� negated� state� before� an� Ultra� DMA� burst� is� initiated.�

�d)� The� device� shall� assert� DMARQ� to� initiate� an� Ultra� DMA� burst.� After� assertion� of� DMARQ� the� device� shall� not�

�negate� DMARQ� until� after� the� first� negation� of� DSTROBE.�

�e)� Steps� I,� (d),� and� (e)� may� occur� in� any� order� or� at� the� same� time.� The� host� shall� assert� STOP.�

�f)�

�The� host� shall� negate� –� HDMARDY.�

�g)� The� host� shall� negate� –� CS0,� -CS1,� A2,� A1,� and� A0.� The� host� shall� keep� –� CS0,� -CS1,� A2,� A1,� and� A0� negated�

�until� after� negating� –� DMACK� at� the� end� of� the� burst.�

�h)� Steps� I,� (d),� and� (e)� shall� have� occurred� at� least� t� ACK� before� the� host� asserts� –� DMACK.� The� host� shall� keep� –�

�DMACK� asserted� until� the� end� of� an� Ultra� DMA� burst.�

�i)�

�j)�

�The� host� shall� release� D[15:0]� within� t� AZ� after� asserting� –� DMACK.�

�The� device� may� assert� DSTROBE� t� ZIORDY� after� the� host� has� asserted� –� DMACK.� Once� the� device� has� driven�

�DSTROBE� the� device� shall� not� release� DSTROBE� until� after� the� host� has� negated� –� DMACK� at� the� end� of� an�

�Ultra� DMA� burst.�

�Swissbit� AG�

�Industriestrasse� 4�

�Swissbit� reserves� the� right� to� change� products� or� specifications� without� notice.�

�Revision:� 1.00�

�CH-9552� Bronschhofen�

�Switzerland�

�www.swissbit.com�

�industrial@swissbit.com�

�C-440_data_sheet_CF-HxBU_Rev100.doc�

�Page� 30� of� 102�

�相关PDF资料 |

PDF描述 |

|---|---|

| F3M-S1213 | SENSOR COMB 12" WAFER 13 SLOTS |

| MX3AWT-A1-0000-0007B8 | LED XLAMP WARM WHITE 350MA 2PLCC |

| MX3AWT-A1-0000-0007AA | LED XLAMP WARM WHITE 350MA 2PLCC |

| MX3SWT-A1-0000-0008B6 | LED XLAMP MX3S WHITE PLCC |

| MX3SWT-A1-0000-0008B5 | LED XLAMP MX3S WHITE PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SFCF4096H2BU4TO-I-MS-527-STD | 制造商:SWISSBIT NA INC 功能描述:FLASH |

| SFCF4096H4BK2SA-C-QT-553-SMA | 制造商:SWISSBIT NA INC 功能描述:FLASH |

| SFCF4096H4BK2SAIQT553SMA | 制造商:Swissbit 功能描述:Flash Card 4G-Byte 3.3V/5V CompactFlash |

| SFCF4096H4BK2SA-I-QT-553-SMA | 功能描述:FLASH SLC UDMA/MDMA/PIO 4G RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-300 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD? |

| SFCF64GBH2BU4TO-C-NU-527-STD | 制造商:SWISSBIT 功能描述:CFC C-440 DENSITY COMMERCIAL - Trays 制造商:SWISSBIT NA INC 功能描述:FLASH |

发布紧急采购,3分钟左右您将得到回复。