- 您现在的位置:买卖IC网 > PDF目录98081 > SL23EP08SC-2HT 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 PDF资料下载

参数资料

| 型号: | SL23EP08SC-2HT |

| 元件分类: | 时钟及定时 |

| 英文描述: | 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封装: | 0.150 INCH, ROHS COMPLIANT,SOIC-16 |

| 文件页数: | 16/18页 |

| 文件大小: | 405K |

| 代理商: | SL23EP08SC-2HT |

Rev 2.0, May 28, 2008

Page 7 of 18

SL23EP08

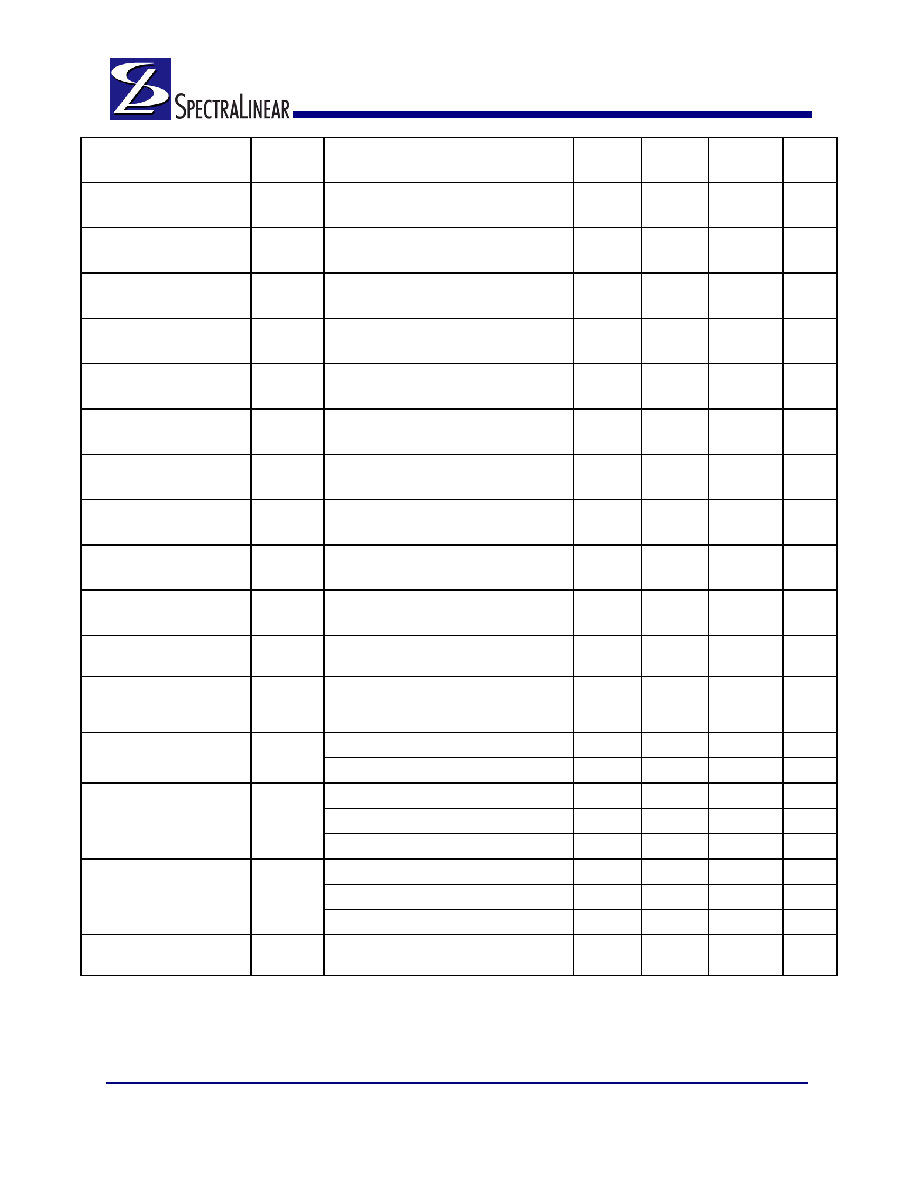

Output Duty Cycle

DC3

CL=15pF, Fout=66 MHz, all versions

Measured at VDD/2

45

50

55

%

Output Duty Cycle

DC4

CL=15pF, Fout=133 MHz, all versions

Measured at VDD/2

45

50

55

%

Output Duty Cycle

DC5

CL=15pF, Fout=166 MHz, all versions

Measured at VDD/2

45

50

55

%

Output Rise/Fall Time

tr/f1

CL=30pF, -1, -2, -3 and -4 versions

0.8V to 2.0V

-

2.2

ns

Output Rise/Fall Time

tr/f2

CL=15pF, -1, -2, -3 and -4 versions

0.8V to 2.0V

-

1.5

ns

Output Rise/Fall Time

tr/f3

CL=30pF, -1H and -2H and versions

0.8V to 2.0V

-

1.5

ns

Output Rise/Fall Time

tr/f4

CL=15pF, -1H and -2H and versions

0.8V to 2.0V

-

1.2

ns

Output-to-Output Skew

on Same Bank

SKW2

-1 and -2, measured from 0.8V to

2.0V, and outputs are equally loaded

-

80

170

ps

Output-to-Output Skew

on Same Bank

SKW2

-1H and -2H and -4, measured at

VDD/2 and outputs are equally loaded

-

70

150

ps

Output-to-Output Skew

Between Bank A and B

SKW3

-1, -1H, 2H and -4, measured at

VDD/2 and outputs are equally loaded

-

80

150

ps

Output-to-Output Skew

Between Bank A and B

SKW4

-2, measured at VDD/2 and outputs

are equally loaded

-

130

300

ps

Device-to-Device Skew

SKW5

All versions, measured at VDD/2 and

outputs are equally loaded

-

150

400

ps

Input-to-Output Delay

Dt

All versions, CLKIN to FBK rising

edge, measured at VDD/2 and outputs

are equally loaded and S2=S1=1

-200

-

200

ps

Fout=33 to 200MHz and CL=15pF

-

100

ps

Cycle-to-Cycle Jitter

(-1 and -1H Versions)

CCJ1

Fout=33 to 200 MHz and CL=30pF

-

150

ps

Fout=66 MHz and CL=15pF

-

200

ps

Fout=66MHz and CL=30pF

-

200

ps

Cycle-to-Cycle Jitter

(-4 and -5 Versions)

CCJ2

Fout=166MHz and CL=15pF

-

200

ps

Fout=66 MHz and CL=15pF

-

400

ps

Fout=133MHz and CL=30pF

-

400

ps

Cycle-to-Cycle Jitter

(-2, -2H and -3 Versions)

CCJ3

Fout=166MHz and CL=15pF

-

400

ps

PLL Lock Time

tLOCK

From 0.95VDD and valid clock

presented at CLKIN

-

1.0

ms

相关PDF资料 |

PDF描述 |

|---|---|

| SL23EP08ZC-1T | PLL BASED CLOCK DRIVER, PDSO16 |

| SL23EP08SI-2 | 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| SL23EP08SC-4 | 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| SL23EP08SC-2T | 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| SL23EP08SI-1H | 23EP SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SL23EP08SC-2T | 功能描述:时钟缓冲器 10-220MHz 8 Outputs ZDB 3.3-2.5V RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| SL23EP08SC-3 | 功能描述:时钟缓冲器 10-220MHz 8 Outputs ZDB 3.3-2.5V RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| SL23EP08SC-3T | 功能描述:时钟缓冲器 10-220MHz 8 Outputs ZDB 3.3-2.5V RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| SL23EP08SC-4 | 功能描述:时钟缓冲器 10-220MHz 8 Outputs ZDB 3.3-2.5V RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

| SL23EP08SC-4H | 功能描述:时钟缓冲器 10-220MH 8 Outputs ZDB 3.3-2.5V RoHS:否 制造商:Texas Instruments 输出端数量:5 最大输入频率:40 MHz 传播延迟(最大值): 电源电压-最大:3.45 V 电源电压-最小:2.375 V 最大功率耗散: 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LLP-24 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。