- 您现在的位置:买卖IC网 > PDF目录98083 > SM320C6701GLPW16 (TEXAS INSTRUMENTS INC) 32-BIT, 167 MHz, OTHER DSP, CBGA429 PDF资料下载

参数资料

| 型号: | SM320C6701GLPW16 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 32-BIT, 167 MHz, OTHER DSP, CBGA429 |

| 封装: | CERAMIC, BGA-429 |

| 文件页数: | 19/62页 |

| 文件大小: | 873K |

| 代理商: | SM320C6701GLPW16 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

SMJ320C6701

FLOATINGPOINT DIGITAL SIGNAL PROCESSOR

SGUS030A – APRIL 2000 – REVISED APRIL 2001

26

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

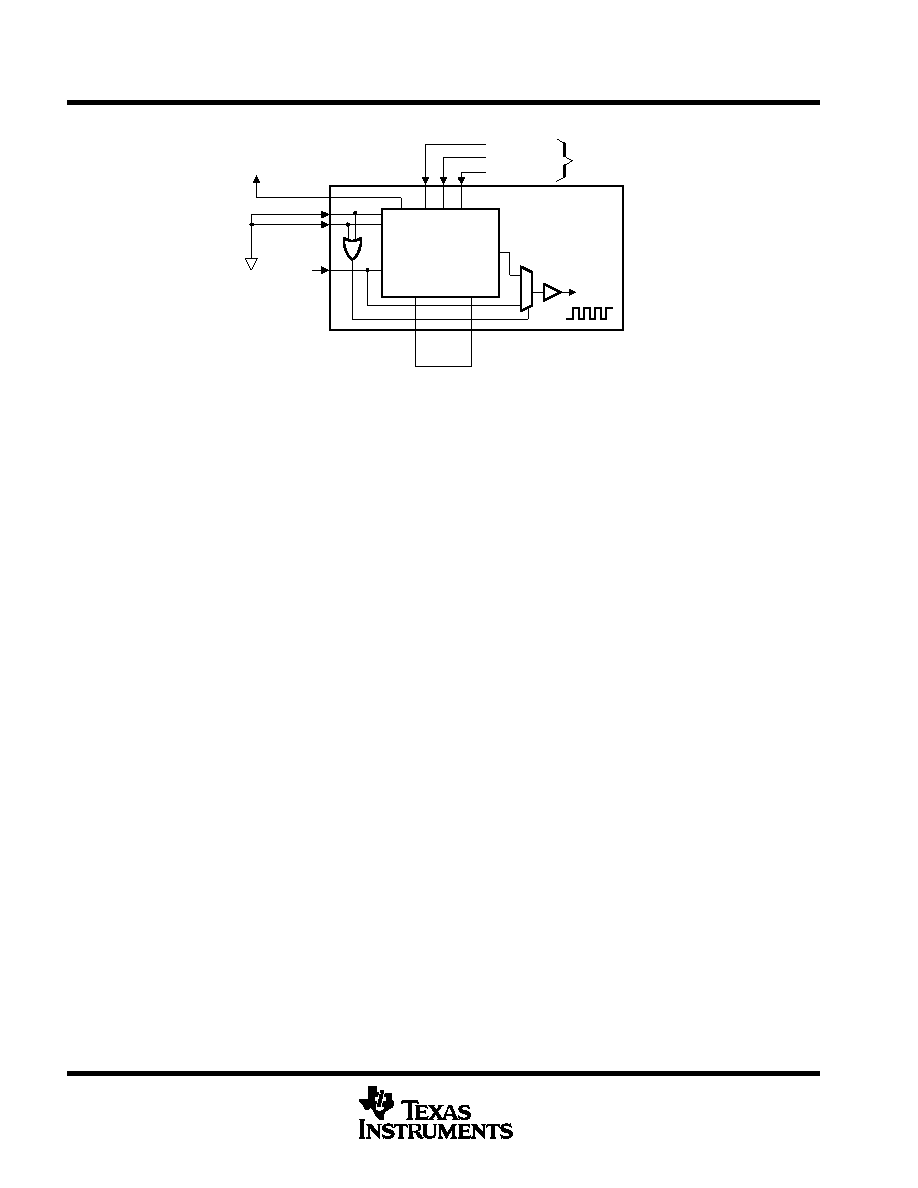

clock PLL (continued)

CLKMODE0

CLKMODE1

PLL

PLLV

CLKIN

LOOP FILTER

PLLCLK

PLLMULT

CLKIN

PLLG

Internal to ’C6701

CPU

CLOCK

PLLF

1

0

3.3V

(see Table 3)

PLLFREQ1

PLLFREQ2

PLLFREQ3

NOTES: A. For a system with ONLY PLL x1 (bypass) mode, short the PLLF terminal to the PLLG terminal.

B. The 3.3-V supply for the EMI filter must be from the same 3.3-V power plane supplying the I/O voltage, DVDD.

Figure 6. External PLL Circuitry for x1 (Bypass) Mode Only

power-supply sequencing

TI DSPs do not require specific power sequencing between the core supply and the I/O supply. However,

systems should be designed to ensure that neither supply is powered up for extended periods of time if the other

supply is below the proper operating voltage.

system-level design considerations

System-level design considerations, such as bus contention, may require supply sequencing to be

implemented. In this case, the core supply should be powered up at the same time as, or prior to (and powered

down after), the I/O buffers. This is to ensure that the I/O buffers receive valid inputs from the core before the

output buffers are powered up, thus, preventing bus contention with other chips on the board.

power-supply design considerations

For systems using the C6000

DSP platform of devices, the core supply may be required to provide in excess

of 2 A per DSP until the I/O supply is powered up. This extra current condition is a result of uninitialized logic

within the DSP(s) and is corrected once the CPU sees an internal clock pulse. With the PLL enabled, as the

I/O supply is powered on, a clock pulse is produced stopping the extra current draw from the supply. With the

PLL disabled, an external clock pulse may be required to stop this extra current draw. A normal current state

returns once the I/O power supply is turned on and the CPU sees a clock pulse. Decreasing the amount of time

between the core supply power up and the I/O supply power up can minimize the effects of this current draw.

A dual-power supply with simultaneous sequencing, such as available with TPS563xx controllers or PT69xx

plug-in power modules, can be used to eliminate the delay between core and I/O power up [see the Using the

TPS56300 to Power DSPs application report (literature number SLVA088)]. A Schottky diode can also be used

to tie the core rail to the I/O rail, effectively pulling up the I/O power supply to a level that can help initialize the

logic within the DSP.

Core and I/O supply voltage regulators should be located close to the DSP (or DSP array) to minimize

inductance and resistance in the power delivery path. Additionally, when designing for high-performance

applications utilizing the C6000

platform of DSPs, the PC board should include separate power planes for

core, I/O, and ground, all bypassed with high-quality low-ESL/ESR capacitors.

相关PDF资料 |

PDF描述 |

|---|---|

| SM320C6701GLPS14 | 32-BIT, 140 MHz, OTHER DSP, CBGA429 |

| SM320C80GFM40 | 64-BIT, 80 MHz, OTHER DSP, CPGA305 |

| SM320F2812HFGM | 16-BIT, 150 MHz, OTHER DSP, CQFP172 |

| SM320MCM41DHFHM40 | 32-BIT, 40 MHz, OTHER DSP, CQFP352 |

| SM320MCM42CHFNM40 | 32-BIT, 40 MHz, OTHER DSP, CQFP408 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SM320C6701S14 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6701S16 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6701W14 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6701W16 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FLOATING-POINT DIGITAL SIGNAL PROCESSOR |

| SM320C6701ZMBW14 | 功能描述:数字信号处理器和控制器 - DSP, DSC Floating Point Dig Signal Proc Military RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。