- 您现在的位置:买卖IC网 > PDF目录98083 > SM320MCM42CHFNM40 (TEXAS INSTRUMENTS INC) 32-BIT, 40 MHz, OTHER DSP, CQFP408 PDF资料下载

参数资料

| 型号: | SM320MCM42CHFNM40 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 32-BIT, 40 MHz, OTHER DSP, CQFP408 |

| 封装: | TIE-BAR, CERAMIC, QFP-408 |

| 文件页数: | 17/22页 |

| 文件大小: | 358K |

| 代理商: | SM320MCM42CHFNM40 |

SMJ320MCM42C, SMJ320MCM42D

DUAL SMJ320C40 MULTICHIP MODULE

SGKS001D – JULY 1997 – REVISED OCTOBER 2001

4

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

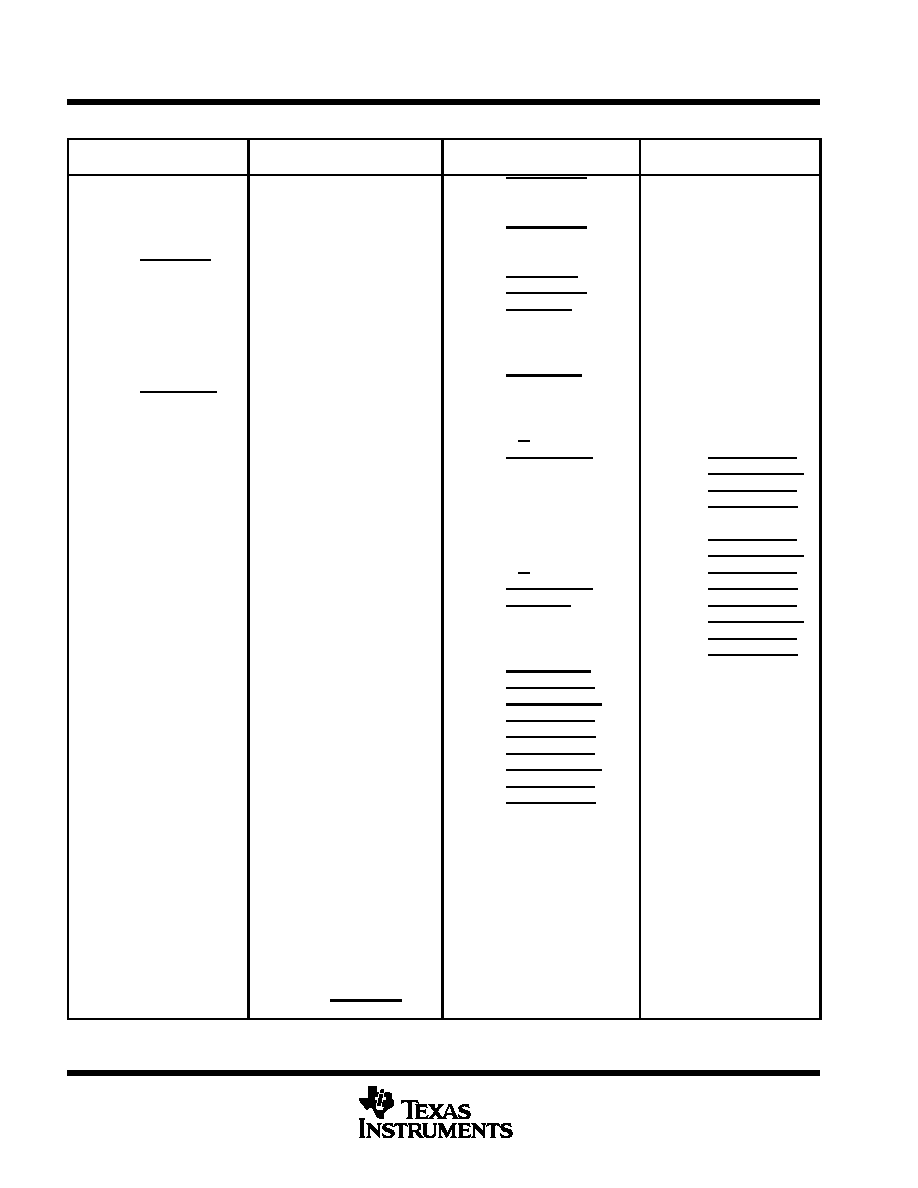

Terminal Assignments

TERMINAL

NO.

NAME

NO.

NAME

NO.

NAME

NO.

NAME

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

ROMEN_C40_#1

IIOF0_C40_#1

IIOF1_C40_#1

IIOF2_C40_#1

IIOF3_C40_#1

NMI_C40_#1

VCC_DR

VSS_CL

TCLK0_C40_#1

TCLK1_C40_#1

H3_C40_#1

H1_C40_#1

VSS_CL

IACK_C40_#1

CLKIN_COMM

VCC_DR

VCC_CL

VCC_DR

VSS_CL

VSS_DR

VCC_DR

VCC_CL

VSS_CL

VSS_DR

VSS_CL

VCC_DR

A30_C40_#1

A29_C40_#1

A28_C40_#1

VCC_DR

A27_C40_#1

A26_C40_#1

A25_C40_#1

A24_C40_#1

A23_C40_#1

A22_C40_#1

A21_C40_#1

A20_C40_#1

A19_C40_#1

A18_C40_#1

A17_C40_#1

VCC_DR

VSS_CL

VSS_DR

A16_C40_#1

A15_C40_#1

A14_C40_#1

A13_C40_#1

A12_C40_#1

A11_C40_#1

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

A10_C40_#1

A9_C40_#1

A8_C40_#1

A7_C40_#1

A6_C40_#1

A5_C40_#1

A4_C40_#1

VCC_DR

A3_C40_#1

A2_C40_#1

A1_C40_#1

A0_C40_#1

D31_C40_#2

D30_C40_#2

D29_C40_#2

D28_C40_#2

D27_C40_#2

D26_C40_#2

VCC_DR

D25_C40_#2

D24_C40_#2

D23_C40_#2

D22_C40_#2

D21_C40_#2

D20_C40_#2

D19_C40_#2

D18_C40_#2

D17_C40_#2

D16_C40_#2

VSS_CL

VCC_DR

VSS_DR

D15_C40_#2

D14_C40_#2

D13_C40_#2

D12_C40_#2

D11_C40_#2

D10_C40_#2

D9_C40_#2

D8_C40_#2

D7_C40_#2

D6_C40_#2

D5_C40_#2

VCC_DR

D4_C40_#2

D3_C40_#2

D2_C40_#2

D1_C40_#2

D0_C40_#2

CE1_C40_#2

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

RDY1_C40_#2

VSS_DR

VSS_CL

LOCK_C40_#2

VCC_CL

VSS_CL

CE0_C40_#2

RDY0_C40_#2

DE_C40_#2

TCK_COMM

TDO_C40_#2

TMS_COMM

TRST_COMM

EMU0_COMM

EMU1_COMM

PAGE1_C40_#2

R/W1_C40_#2

STRB1_C40_#2

STAT0_C40_#2

STAT1_C40_#2

VSS_CL

STAT2_C40_#2

STAT3_C40_#2

PAGE0_C40_#2

R/W0_C40_#2

STRB0_C40_#2

AE_C40_#2

RESETLOC1_C40_#2

VCC_DR

RESETLOC0_C40_#2

RESET_COMM

CRDY5_C40_#2

CSTRB5_C40_#2

CACK5_C40_#2

CREQ5_C40_#2

CRDY4_C40_#2

CSTRB4_C40_#2

CACK4_C40_#2

CREQ4_C40_#2

VCC_DR

C5D7_C40_#2

C5D6_C40_#2

C5D5_C40_#2

C5D4_C40_#2

C5D3_C40_#2

C5D2_C40_#2

C5D1_C40_#2

C5D0_C40_#2

VCC_DR

C4D7_C40_#2

C4D6_C40_#2

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

C4D5_C40_#2

C4D4_C40_#2

C4D3_C40_#2

C4D2_C40_#2

C4D1_C40_#2

C4D0_C40_#2

VCC_DR

VSS_CL

C2D7_C40_#2

C2D6_C40_#2

C2D5_C40_#2

C2D4_C40_#2

C2D3_C40_#2

C2D2_C40_#2

C2D1_C40_#2

C2D0_C40_#2

CRDY2_C40_#2

CSTRB2_C40_#2

CACK2_C40_#2

CREQ2_C40_#2

VCC_DR

CRDY1_C40_#2

CSTRB1_C40_#2

CACK1_C40_#2

CREQ1_C40_#2

CRDY0_C40_#2

CSTRB0_C40_#2

CACK0_C40_#2

CREQ0_C40_#2

VSS_DR

VSS_CL

VSS_DR

VCC_DR

C1D7_C40_#2

C1D6_C40_#2

C1D5_C40_#2

C1D4_C40_#2

C1D3_C40_#2

C1D2_C40_#2

C1D1_C40_#2

C1D0_C40_#2

VCC_DR

C0D7_C40_#2

C0D6_C40_#2

C0D5_C40_#2

C0D4_C40_#2

C0D3_C40_#2

C0D2_C40_#2

C0D1_C40_#2

C0D0_C40_#2

相关PDF资料 |

PDF描述 |

|---|---|

| SM320VC33HFGM150 | 32-BIT, 75 MHz, OTHER DSP, CQFP164 |

| SM34020AHTM32 | GRAPHICS PROCESSOR, CQFP132 |

| SM563 | 4-BIT, MROM, MICROCONTROLLER, PQFP64 |

| SM565 | 4-BIT, MROM, MICROCONTROLLER, PQFP100 |

| SM5K7 | 4-BIT, MROM, MICROCONTROLLER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SM320VC33 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| SM320VC33-EP | 制造商:TI 制造商全称:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| SM320VC33GNLM150 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| SM320VC33GNMM150 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| SM320VC33GNMM150EP | 功能描述:数字信号处理器和控制器 - DSP, DSC EP Digital Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。