- 您现在的位置:买卖IC网 > PDF目录98083 > SMJ320C26FJ (TEXAS INSTRUMENTS INC) 16-BIT, 40 MHz, OTHER DSP, CQCC68 PDF资料下载

参数资料

| 型号: | SMJ320C26FJ |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 16-BIT, 40 MHz, OTHER DSP, CQCC68 |

| 封装: | CERAMIC, LCC-68 |

| 文件页数: | 16/40页 |

| 文件大小: | 577K |

| 代理商: | SMJ320C26FJ |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

SMJ320C26

DIGITAL SIGNAL PROCESSOR

SGUS 016A – AUGUST 1990 – REVISED AUGUST 2001

23

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

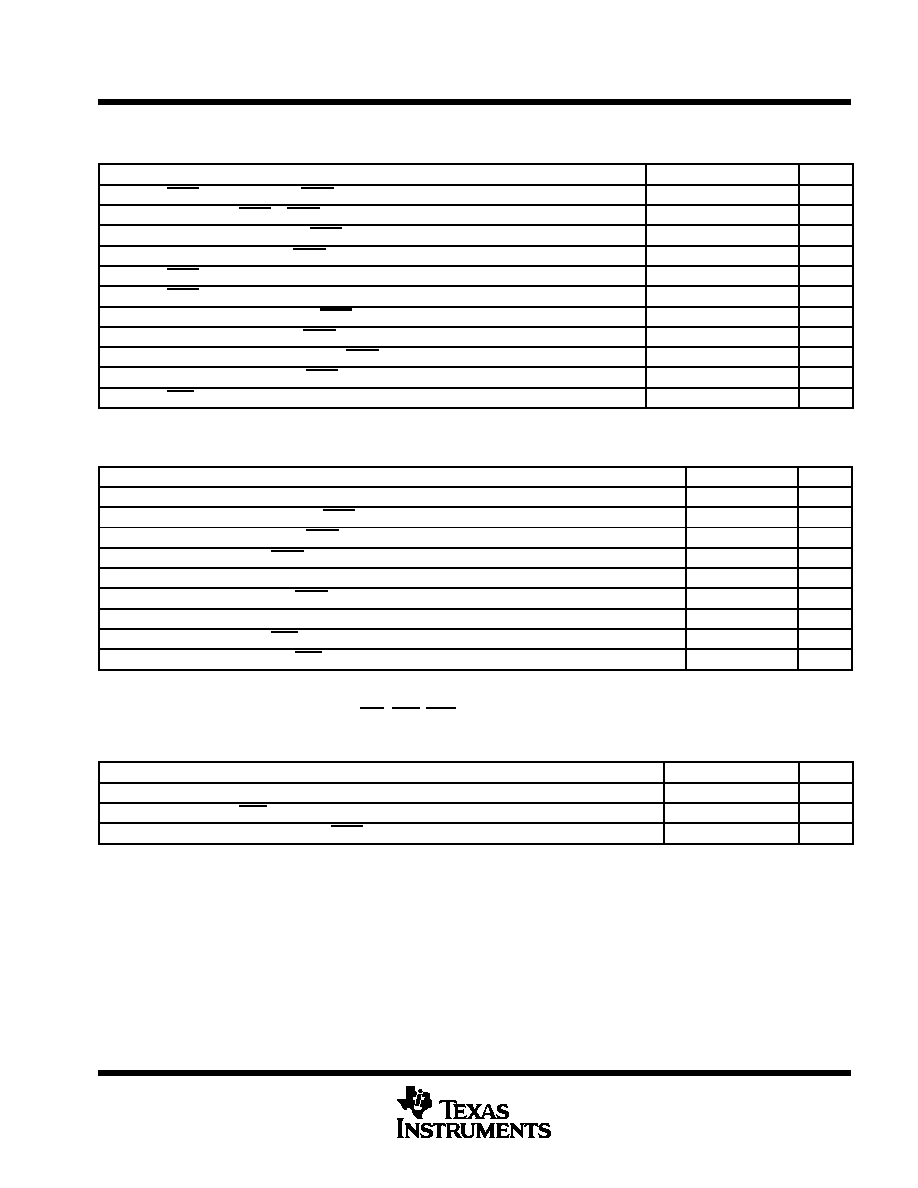

MEMORY AND PERIPHERAL INTERFACE TIMING

switching characteristics over recommended operating conditions (see Note 1)

PARAMETER

MIN

TYP

MAX

UNIT

td(C1-S)

STRB from CLKOUT1 (if STRB is present)

Q – 6

Q

Q+6

ns

td(C2-S)

CLKOUT2 to STRB (if STRB is present)

– 6

0

6

ns

tsu(A)

Address setup time before STRB low (see Note 3)

Q – 12

ns

th(A)

Address hold time after STRB high (see Note 3)

Q – 8

ns

tw(SL)

STRB low pulse duration (no wait states, see Note 4)

2Q – 5

2Q

2Q + 5

ns

tw(SH)

STRB high pulse duration (between consecutive cycles, see Note 4)

2Q

ns

tsu(D)W

Data write setup time before STRB high (no wait states)

2Q – 20

ns

th(D)W

Data write hold time from STRB high

Q – 10

Q

ns

ten(D)

Data bus starts being driven after STRB low (write cycle)

0

ns

tdis(D)

Data bus three-state after STRB high (write cycle)

Q

Q+15

ns

td(MSC)

MSC valid from CLKOUT1

– 10

0

10

ns

This parameter is not production tested.

timing requirements over recommended operating conditions (see Note 1)

MIN

MAX

UNIT

ta(A)

Read data access time from address time (read cycle) (see Notes 3 and 5)

3Q – 40

ns

tsu(D)R

Data read setup time before STRB high

23

ns

th(D)R

Data read hold time from STRB high

0

ns

td(SL-R)

READY valid after STRB low (no wait states)

Q – 22

ns

td(C2H-R) READY valid after CLKOUT2 high

Q – 22

ns

th(SL-R)

READY hold time after STRB low (no wait states)

Q+3

ns

th(C2H-R) READY hold after CLKOUT2 high

Q+3

ns

td(M-R)

READY valid after MSC valid

2Q –25

ns

th(M-R)

READY hold time after MSC valid

0

ns

This parameter is not production tested.

RS, INT, BIO, AND XF TIMING

switching characteristics over recommended operating conditions (see Note 1)

PARAMETER

MIN

TYP

MAX

UNIT

td(RS)

CLKOUT1 low to reset state entered

22

ns

td(IACK)

CLKOUT1 to IACK valid

– 8

0

8

ns

td(XF)

XF valid before falling edge of STRB

Q – 12

ns

相关PDF资料 |

PDF描述 |

|---|---|

| SMJ320C31KGDM40B | 32-BIT, 40 MHz, OTHER DSP, UUC132 |

| SMJ320C40KGDS50C | 32-BIT, 50 MHz, OTHER DSP, UUC325 |

| SMJ320C40TABM40/10 | 32-BIT, 40 MHz, OTHER DSP, UUC325 |

| SM320C40TABS60/10 | 32-BIT, 60 MHz, OTHER DSP, UUC325 |

| SMJ320C6201BGLPW20 | 32-BIT, 200 MHz, OTHER DSP, CBGA429 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SMJ320C30 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| SMJ320C30-40 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| SMJ320C30-50 | 制造商:TI 制造商全称:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| SMJ320C30GB | 制造商:TI 制造商全称:Texas Instruments 功能描述:DIGITAL SIGNAL PROCESSOR |

| SMJ320C30GBM40 | 功能描述:数字信号处理器和控制器 - DSP, DSC Digital Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。