- 您现在的位置:买卖IC网 > PDF目录67997 > SMJL-29C80F/883 (ATMEL CORP) 12-BIT, DSP-FAST COSINE TRANSFRM PROCESSOR, CQCC44 PDF资料下载

参数资料

| 型号: | SMJL-29C80F/883 |

| 厂商: | ATMEL CORP |

| 元件分类: | 数字信号处理外设 |

| 英文描述: | 12-BIT, DSP-FAST COSINE TRANSFRM PROCESSOR, CQCC44 |

| 封装: | MQFP-44 |

| 文件页数: | 1/18页 |

| 文件大小: | 287K |

| 代理商: | SMJL-29C80F/883 |

29C80F

Rev. D (25 Mar.97)

65

MATRA MHS

Introduction

The 29C80F is a dedicated two-dimensional discrete

cosine transform circuit. The two-dimensional forward

transform (FDCT) or inverse transform (IDCT) is

performed on fixed 8

× 8 pixel or coefficient blocks (64

samples).

These blocks can be scanned from left to right, line by

line, or up to down, column by column, or in zig-zag order

for coefficient blocks only. If the input matrix is scanned

line by line and if the zig-zag order is not used, then the

output

matrix

will

appear

column

by

column

(line/column transposition between inputs and outputs).

For FDCT, the input bus receives pixels coded with 8 or

9 bit in two’s complement format and the 29C80F output

coefficients are coded with 12 bit in two’s complement

format..

For IDCT, the input bus receives coefficients coded with

12 bit in two’s complement format and the 29C80F output

pixels are coded with 8 or 9 bit in two’s complement

format.

A parallel architecture and a DCT based on modified

CHEN algorithm are used allowing high precision

compatible with the CCITT H261 requirements for

accuracy and fast operation up to 20 Mpixels/s.

Except for clock circuitry, the 29C80F is composed of 5

blocks :

– 2 identical 1D DCT processors (line DCT and column

DCT).

– 1 memory for line/column transposition (between the 2

DCT processors).

– 1 memory for zig-zag scanning.

– 1 clipping operator (following the column DCT

processor).

All the internal sequencers are reset then started by a

pipelined signal, BLKIN (Block Input), and stopped after

a fixed number of cycles. The BLKOUT (Block Output)

signal indicates the beginning of a block on the output

data bus DO[0..11].

The latent period (the time between input data and its

corresponding output result) is 128 CLK cycles

(regardless of zig-zag scanning selection). The 29C80F

has been designed to process contiguous blocks.

However, it is possible to introduce a gap period between

two blocks and/or to mix FDCT/IDCT by respecting

some recommendations.

The 29C80F is designed to cover a wide range of real time

DCT coding/decoding applications up to 20 MSamples/s.

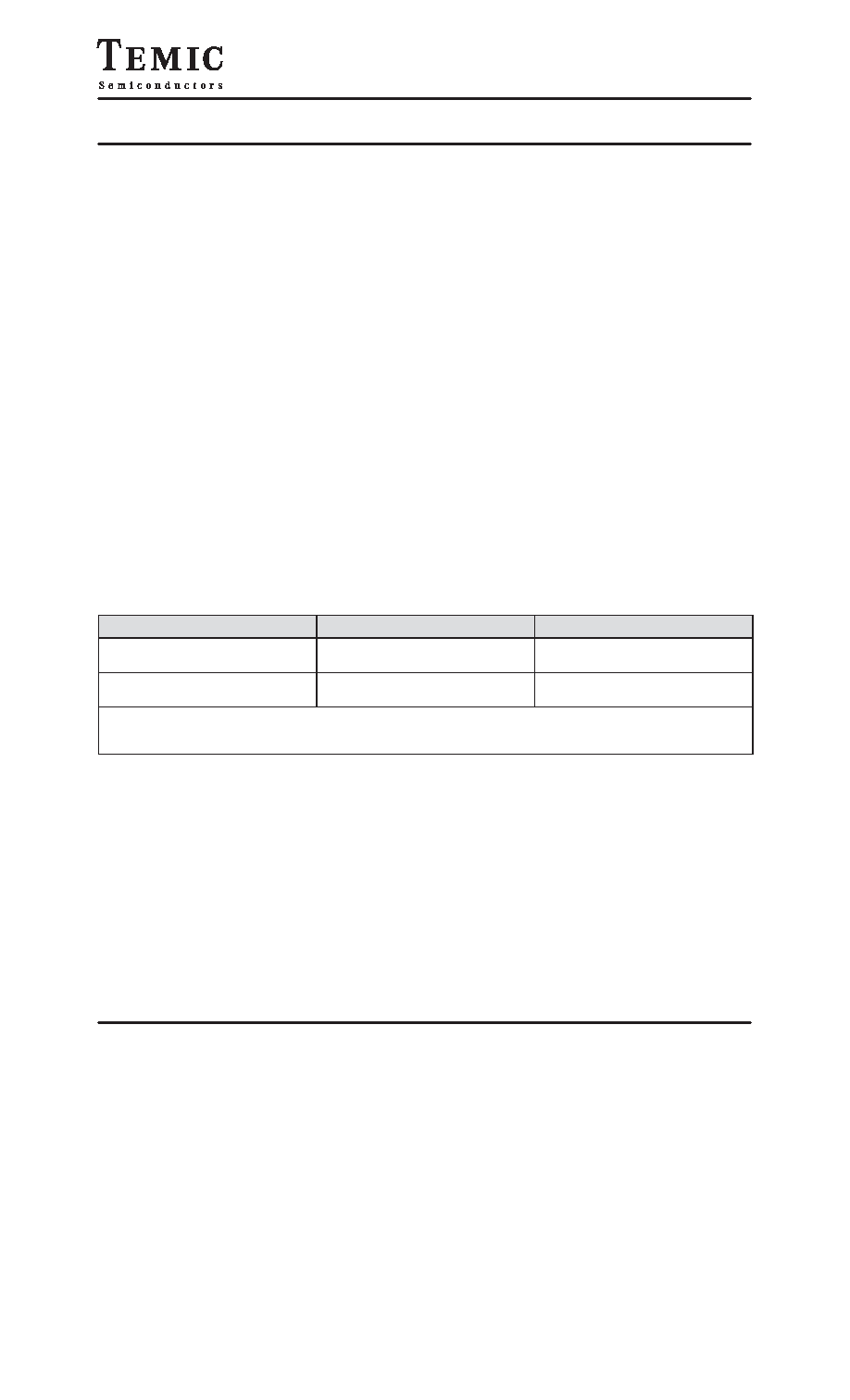

Input Data Bus(1)

Output Data Bus(1)

FDCT

Pixels 8-bit : DI [11..4](2)

Pixels 9-bit : DI[11..3](3)

Coefficients : DO[11..0]

IDCT

Coefficients : DO[11..0]

Pixels 8-bit : DI[11..4](4)

Pixels 9-bit : DI[11..3](5)

Notes :

1. Data coded with 2’s complement

4. DO[3..0] forced to VOL

2. DI[3..0] must be tied to VIL

5. DO[2..0] forced to VOL

3. DI[2..0] must be tied to VIL

Features

D Forward and inverse 8 × 8 data transform

D DC to 20 MHz pixel rate (20 MHz clock)

D 9 bit two’s complement pixel format

D 8 bit two’s complement pixel format with optimised

accuracy

D 12 bit two’s complement coefficient format

D Fully compliant with CCITT H261 accuracy

D Selectable zig-zag scanning for coefficient blocks

D Full parallel architecture

D Radiation tolerant for space application

D Fully synchronous interface

D 128 block cycles latency

D Power down mode

D Tristate control output

D TTL compatible inputs and outputs

D Single 5 V ± 10 % power supply

D 44 pin MQFPJ

D Advanced 0.8 m CMOS technology

2D Discrete Cosine Transform Circuit

相关PDF资料 |

PDF描述 |

|---|---|

| SMJL-29C80FSC | 12-BIT, DSP-FAST COSINE TRANSFRM PROCESSOR, CQCC44 |

| MPC107APX066L0 | MULTIFUNCTION PERIPHERAL, PBGA503 |

| MPC107ARX066L0 | MULTIFUNCTION PERIPHERAL, CBGA503 |

| MPC555LFMZP40R2 | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PBGA272 |

| MPC555LFAZP40 | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PBGA272 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SMJP-1V04W1P1 | 制造商:SEOUL 制造商全称:Seoul Semiconductor 功能描述:Acrich2 - 100V 4.3W MR Connect using a AIC directly to AC power |

| SMJP-1V04W1P1-XX | 制造商:Seoul Semiconductor 功能描述:ACRICH2 - Bulk |

| SMJP-2V04W1P1 | 制造商:SEOUL 制造商全称:Seoul Semiconductor 功能描述:Acrich 2 - 120V 4.3W MR Connect using a AIC directly to AC power |

| SMJP-2V04W1P1-G | 制造商:Seoul Semiconductor 功能描述: |

| SMJP-2V04W1P1-XX | 制造商:Seoul Semiconductor 功能描述:ACRICH2 - Bulk |

发布紧急采购,3分钟左右您将得到回复。