- 您现在的位置:买卖IC网 > PDF目录193594 > SP674AA 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP28 PDF资料下载

参数资料

| 型号: | SP674AA |

| 元件分类: | ADC |

| 英文描述: | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP28 |

| 封装: | 0.600 INCH, CERDIP-28 |

| 文件页数: | 11/14页 |

| 文件大小: | 204K |

| 代理商: | SP674AA |

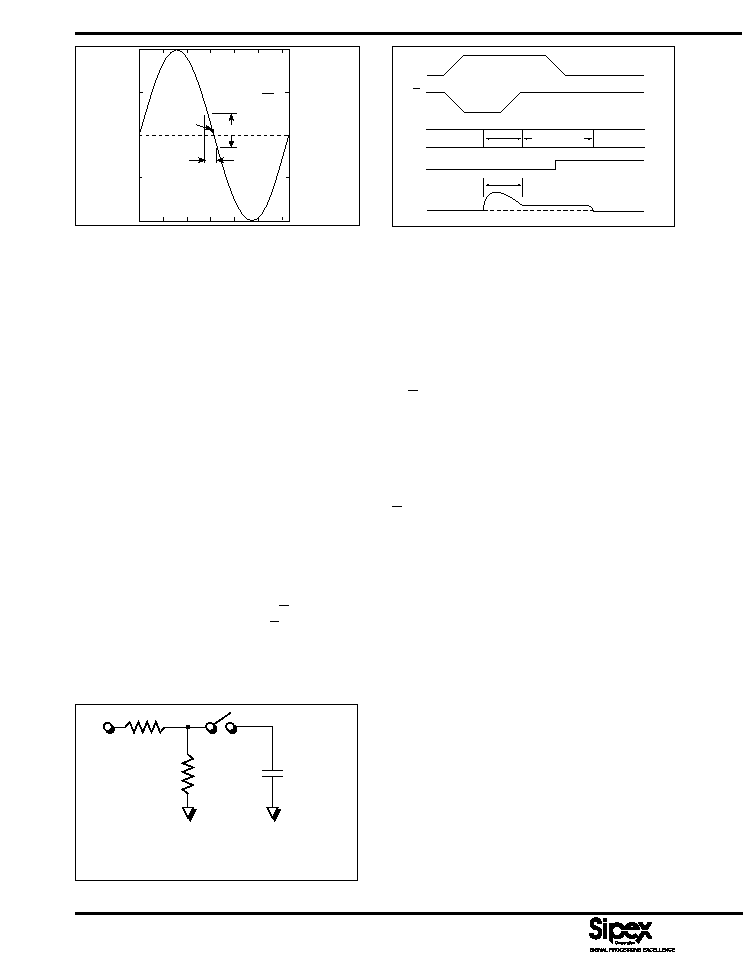

8

R/C

CE

WAIT FOR

CONVERT SIGNAL

WAIT FOR

BUS READ

CONVERSION

VIN

CDAC VOLTAGE

0 VOLTS

t(ACQ)

ACQUISITION

TIME

ACQUISITION TIME =

APERTURE DELAY TIME =

0.12 x tCONVERT

the input which will upset the buffer output and

may add error to the conversion itself.

Furthermore, the isolation of the input after the

acquisition time in the HS574A/SP674A allows

the user an opportunity to release the hold on an

external sample-and-hold and start it tracking

the next sample. This will increase system

throughput with the user's existing components.

When using an external S/H, the HS574A/

SP674A acts as any other 574–type device be-

cause the internal S/H is transparent. The sample/

hold function in the HS574A/SP674A is inher-

ent to the capacitor DAC structure, and its timing

characteristics are determined by the internally

generated clock. However, for multiplexer op-

eration, the internal S/H may eliminate the need

for an external S/H. The operation of the S/H

function is internal to the HS574A/SP674A and

is controlled through the normal R/C control line

(refer to Figure 3). When the R/C line makes a

negative transition, the HS574A/SP674A starts

the timing of the sampling and conversion. The

first two clock cycles are allocated to signal

Figure 3. Sample–and–Hold Function

Figure 1. Aperture Uncertainty

acquisition of the input by the CDAC (this time

is defined as t

ACQ). Following these two cycles,

the input sample is taken and held. The A/D

conversion follows this cycle with the duration

controlled by the internal clock cycle, which is

determined by the specific product model. Note

that because the sample is taken relative to the

R/C transition, t

ACQ is also the traditional “aper-

ture delay” of this internal sample and hold.

Since

t

ACQ is measured in clock cycles, its

duration will vary with the internal clock

frequency. This results in T

ACQ = 2.9

sec

±1.1secs between units and over temperatures.

Offset, gain and linearity errors of the S/H cir-

cuit, as well as the effects of its droop rate, are

included in the overall specs for the HS574A/

SP674A.

USING THE SPX74A SERIES

Typical Interface Circuit

The HS574A/SP674A is a complete A/D con-

verter that is fully operational when powered up

and issued a Start Convert Signal. Only a few

external components are necessary.

Figure 4

depicts a typical interface circuit for operating

the HS574A/SP674A in a unipolar input mode.

Figure 5 depicts a typical interface circuit for

operating the HS574A/SP674A in a bipolar in-

put mode. Further information is given in the

following sections on these connections, but first

a few considerations concerning board layout to

achieve the best operation.

For each application of this device, strict atten-

tion must be given to power supply decoupling,

board layout (to reduce pickup between analog

VERROR

t

SAMPLE

POINT

VERROR = t dv

dt

25pF

REQ = 4K at any range.

T = REQ x CEQ = 100ns.

Figure 2. Equivalent SP574A Input Circuit

相关PDF资料 |

PDF描述 |

|---|---|

| SP674AB | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP28 |

| SP674AK | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP28 |

| SP674AL | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP28 |

| SP674AS | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP28 |

| SP674AT/883 | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SP674AB | 制造商:SIPEX 制造商全称:Sipex Corporation 功能描述:12-Bit Sampling A/D Converters |

| SP674AC | 制造商:SIPEX 制造商全称:Sipex Corporation 功能描述:12-bit Sampling A/D Converters |

| SP674AJ | 制造商:SIPEX 制造商全称:Sipex Corporation 功能描述:12-bit Sampling A/D Converters |

| SP674AK | 制造商:SIPEX 制造商全称:Sipex Corporation 功能描述:12-bit Sampling A/D Converters |

| SP674AL | 制造商:SIPEX 制造商全称:Sipex Corporation 功能描述:12-bit Sampling A/D Converters |

发布紧急采购,3分钟左右您将得到回复。