- 您现在的位置:买卖IC网 > PDF目录1245 > SPI-324P-O4-N1 (Lattice Semiconductor Corporation)IP PHY LAYER BRIDGE SPI3-4 ORCA4 PDF资料下载

参数资料

| 型号: | SPI-324P-O4-N1 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 6/23页 |

| 文件大小: | 0K |

| 描述: | IP PHY LAYER BRIDGE SPI3-4 ORCA4 |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | SPI324PO4N1 |

�� �

�

Quad� SPI-3� to� SPI-4� Link� Layer�

�Lattice� Semiconductor�

�Bridge� Core� User’s� Guide�

�DPRAM� should� be� programmed� to� the� 3/4� full� +� 1� level� by� setting� the� FIFO_FULL_TYPE_SEL� bit� in� the� FPSC�

�high.�

�When� a� burst� of� data� is� written� into� a� DPRAM,� the� Tx_Port� signals� into� the� ASB� are� set� to� the� port� number.� In� order�

�to� uniquely� identify� data� associated� with� different� SPI-3� interfaces� which� may� have� the� same� port� number� (for�

�example,� if� port� 1� is� used� on� interface� 0� and� port� 1� is� also� used� on� interface� 1),� the� RX� Interface� circuit� will� set� at�

�most� up� to� two� bits� of� the� Tx_Port� value� to� indicate� the� SPI-3� interface� number.� The� bits� which� the� circuit� automati-�

�cally� sets� will� always� be� the� next� most� signi?cant� bits� following� the� port� number.� For� example,� if� the� core� is� con?g-�

�ured� for� 4� SPI-3� interfaces� and� 4� ports� per� interface,� then� Tx_Port[1:0]� will� identify� which� of� four� port� numbers� the�

�data� is� associated� with,� and� Tx_Port[3:2]� will� be� set� by� the� circuit� to� indicate� the� SPI-3� interface� number.� This� fea-�

�ture� is� hardcoded� in� the� circuit� and� cannot� be� disabled.�

�Design� Parameters�

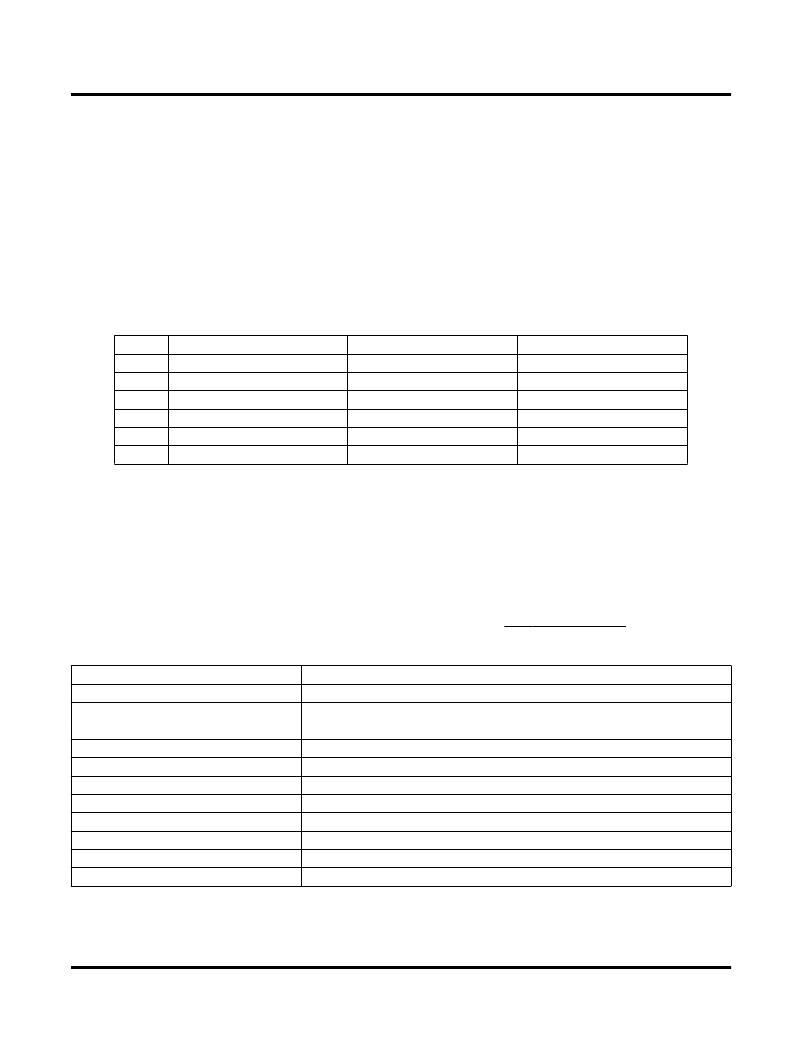

�Table� 1.� Parameters�

�No.�

�1�

�2�

�3�

�4�

�5�

�6�

�Parameter�

�Number� of� SPI-3� Interfaces�

�Burst� Size�

�Number� of� Ports� per� Interface�

�DTPA� Selected�

�PTPA� Selected�

�STPA� Selected�

�Choice�

�1,� 2,� 3,� 4�

�32,� 64,� 128,� 256�

�1,� 2,� 4,� 8�

�Yes/No�

�Yes/No�

�Yes/No�

�Default�

�4�

�32�

�4�

�Yes�

�No�

�No�

�Note:� Only� one� of� the� polling� methods� (DTPA,� STPA,� or� PTPA)� may� be� selected� at� one� time.�

�Register� Interface� Description�

�A� bank� of� registers� are� implemented� to� manage� various� programmable� control� functions� and� store� various� error�

�and� status� signals.� These� registers� are� controlled� by� a� register� interface� that� is� compatible� with� the� ORCA� System�

�Bus� interface.� The� ORCA� SYSBUS� slave� interface� is� instantiated� to� control� the� core� registers.� The� external� FPGA�

�control� interface� is� compatible� with� a� Motorola� MPC860� Power� PC� interface.�

�The� core� maintains� an� 8-bit� implementation� of� the� system� bus.� Details� of� the� operation� of� the� system� bus� are� avail-�

�able� in� Lattice� technical� note� TN1017,� ORCA� Series� 4� MPI/System� Bus,� at� www.latticesemi.com.�

�Table� 2.� Register� Descriptions�

�Register� Name�

�ID/Version� Register�

�Parity� Control� Register�

�Transmit� Parity� Error� Register�

�DPRAM� Read� Provisioning� Register� 0�

�DPRAM� Read� Provisioning� Register� 1�

�DPRAM� Read� Provisioning� Register� 2�

�DPRAM� Read� Provisioning� Register� 3�

�DPRAM� Read� Provisioning� Register� 4�

�DPRAM� Read� Provisioning� Register� 5�

�DPRAM� Read� Provisioning� Register� 6�

�DPRAM� Read� Provisioning� Register� 7�

�Register� Address�

�0x8000�

�0x8001�

�0x8002�

�0x8003�

�0x8004�

�0x8005�

�0x8006�

�0x8007�

�0x8008�

�0x8009�

�0x800A�

�6�

�Description�

�ID/Version� Number� of� Core�

�Selects� Odd� or� Even� parity� on� SPI-3� interface�

�Indicates� parity� error� on� a� SPI-3� interface�

�Selects� Virtual� FIFO� to� be� read� during� cycle� 1� of� 8�

�Selects� Virtual� FIFO� to� be� read� during� cycle� 2� of� 8�

�Selects� Virtual� FIFO� to� be� read� during� cycle� 3� of� 8�

�Selects� Virtual� FIFO� to� be� read� during� cycle� 4� of� 8�

�Selects� Virtual� FIFO� to� be� read� during� cycle� 5� of� 8�

�Selects� Virtual� FIFO� to� be� read� during� cycle� 6� of� 8�

�Selects� Virtual� FIFO� to� be� read� during� cycle� 7� of� 8�

�Selects� Virtual� FIFO� to� be� read� during� cycle� 8� of� 8�

�相关PDF资料 |

PDF描述 |

|---|---|

| SPN02SVBN-RC | CONN JUMPER SHORTING 2MM GOLD |

| SPN02SVEN-RC | CONN JUMPER SHORTING 2MM GOLD |

| SPN02SXCN-RC | CONN JUMPER SHORTING 2MM GOLD |

| SPT711XPFCE | CARD TELEPHONY FARM CRD 711X |

| SPUSB1AJT | SURGE SUPPRESOR USB 12OHM SC70-6 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SPI-333-34AB | 制造商:SANYO Semiconductor Co Ltd 功能描述: |

| SPI-335-34 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Ultraminiature photoreflector (single-transistor type) |

| SPI-336-99-T1 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Ultraminiature photoreflector supporting reflow soldering Single transistor type |

| SPI3501UH | 制造商:SPI 制造商全称:SPI 功能描述:350 Watts EPS12V 1U Switching Power Supply |

| SPI3501UH-B204 | 制造商:Sparkle Power Inc 功能描述:POWER SUPPLY,SWITCHING,ENCLOSED,1U,350 WATT,ATX/EPS,PFC,(2)1 |

发布紧急采购,3分钟左右您将得到回复。