- 您现在的位置:买卖IC网 > PDF目录271213 > SST55LC100-45-C-TQWE FLASH MEMORY DRIVE CONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | SST55LC100-45-C-TQWE |

| 元件分类: | 存储控制器/管理单元 |

| 英文描述: | FLASH MEMORY DRIVE CONTROLLER, PQFP100 |

| 封装: | ROHS COMPLIANT, MS-026AED, TQFP-100 |

| 文件页数: | 3/80页 |

| 文件大小: | 758K |

| 代理商: | SST55LC100-45-C-TQWE |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

Advance Information

CompactFlash Card Controller

SST55LC100

2005 Silicon Storage Technology, Inc.

S71298-00-000

10/05

11

IORD#

(Memory Card mode)

19

F1

I

I3U

This signal is not used in this mode.

IORD#

(PC Card I/O mode)

This is an I/O Read strobe generated by the host. This signal

gates I/O data onto the bus from the CompactFlash card when

the card is configured to use the I/O interface.

IORD#

(True IDE mode)

In True IDE mode, this signal has the same function as in PC

card I/O mode.

IOWR#

(Memory Card mode)

57

H9

I

I3U

This signal is not used in this mode.

IOWR#

(PC Card I/O mode)

The I/O Write strobe pulse is used to clock I/O data on the card

data bus into the CompactFlash card controller registers when

the CompactFlash card is configured to use the I/O interface.

IOWR#

(True IDE mode)

In True IDE mode, this signal has the same function as in PC

Card I/O mode.

OE#

(Memory Card mode)

13

D1

I

I3U

This is an Output Enable strobe generated by the host inter-

face. It is used to read data from the CompactFlash card in

Memory mode and to read the CIS and configuration registers.

OE#

(PC Card I/O mode)

In PC Card I/O mode, this signal is used to read the CIS and

configuration registers.

ATASEL#

(True IDE mode)

To enable True IDE mode this input should be grounded by the

host.

Ready

(Memory Card mode)

21

G1

O

O1

In Memory mode this signal is set high when the Compact-

Flash card is ready to accept a new data transfer operation

and held low when the card is busy.

At power up and at Reset, the Ready signal is held low (busy)

until the CompactFlash card has completed its power up or

reset function. No access of any type should be made to the

CompactFlash card during this time.

IREQ#

(PC Card I/O mode)

I/O Operation - After the CompactFlash card has been config-

ured for I/O operation, this signal is used as Interrupt Request.

This line is strobed low to generate a pulse mode interrupt or

held low for a level mode interrupt.

INTRQ

(True IDE mode)

In True IDE mode signal is the active high Interrupt Request to

the host.

REG#

(Memory Card mode)

20

G2

I

I3U

This signal is used during Memory cycles to distinguish

between Common Memory and Register (Attribute) Memory

Attribute Memory Select accesses. High for Common Memory,

Low for Attribute Memory.

REG#

(PC Card I/O mode)

The signal must also be active (low) during I/O Cycles when

the I/O address is on the Bus.

Reserved

(True IDE mode)

In True IDE mode this input signal is not used and should be

connected to VDD by the host.

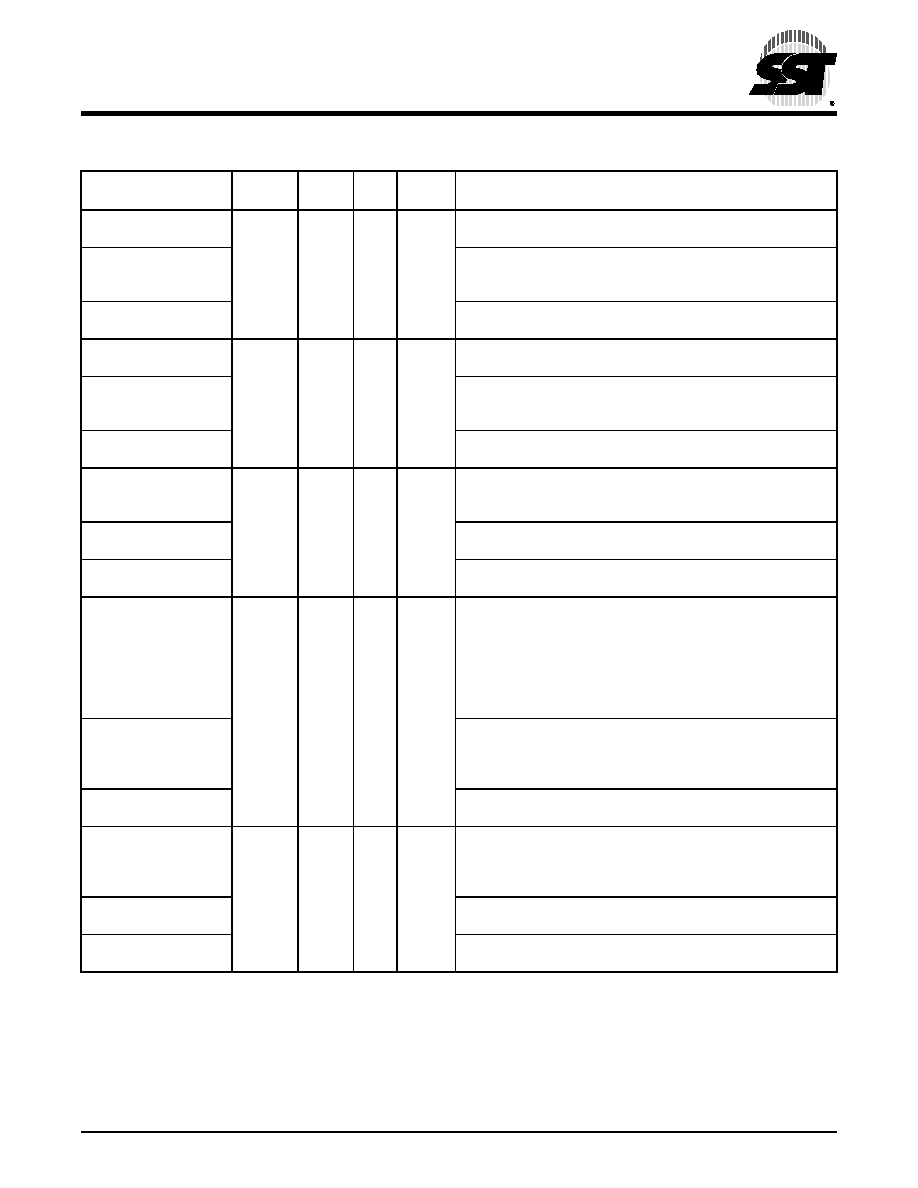

TABLE

3-1: PIN ASSIGNMENTS (CONTINUED) (3 OF 6)

Signal Name

100-lead 84-ball

Pin

Type

I/O

Type1

Name and Functions

相关PDF资料 |

PDF描述 |

|---|---|

| SST89E54RD2A-40-C-TQJE | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP44 |

| SST89E54RD2A-40-I-TQJE | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP44 |

| STM8L151C8T3STM8L151C8T3 | 8-BIT, FLASH, 16 MHz, RISC MICROCONTROLLER, PQFP48 |

| ST7FLITE10BF0B6 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP20 |

| ST7FLITE10BY0B3 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SST55LC100-45-I-BWE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:CompactFlash Card Controller |

| SST55LC100-45-I-TQWE | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:CompactFlash Card Controller |

| SST55LC100M | 制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:CompactFlash Card Controller |

| SST55LC100M-45-C-BWE | 功能描述:总线收发器 Compact Flash 45MHz 3.3V Commercial RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| SST55LC100M-45-C-TQWE | 功能描述:总线收发器 Compact Flash 45MHz 3.3V Commercial RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。