- 您现在的位置:买卖IC网 > PDF目录9712 > SSTUB32S868DHLF (IDT, Integrated Device Technology Inc)IC REGIST BUFF 25BIT DDR2 176BGA PDF资料下载

参数资料

| 型号: | SSTUB32S868DHLF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 15/20页 |

| 文件大小: | 0K |

| 描述: | IC REGIST BUFF 25BIT DDR2 176BGA |

| 产品变化通告: | Product Discontinuation 09/Dec/2011 |

| 标准包装: | 208 |

| 逻辑类型: | DDR2 的寄存缓冲器 |

| 电源电压: | 1.7 V ~ 1.9 V |

| 位数: | 25 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 176-TFBGA |

| 供应商设备封装: | 176-CABGA(6x15) |

| 包装: | 托盘 |

4

ICSSSTUB32S868D

Advance Information

08/14/06

General Description

This 28-bit 1:2 configurable registered buffer is designed for 1.7-V to 1.9-V VDD operation. All inputs are compatible

with the JEDEC standard for SSTL_18, except the chip-select gate-enable (CSGEN), control (C), and reset (RESET)

inputs, which are LVCMOS. All outputs are edge-controlled circuits optimized for unterminated DIMM loads, and meet

SSTL_18 specifications, except the open-drain error (QERR) output.

The ICSSSTUB32S868D operates from a differential clock (CK and CK). Data are registered at the crossing of CK

going high and CK going low. The device supports low-power standby operation. When RESET is low, the differential

input receivers are disabled, and undriven (floating) data, clock, and reference voltage (VREF) inputs are allowed. In

addition, when RESET is low, all registers are reset and all outputs are forced low except QERR. The LVCMOS RESET

and C inputs always must be held at a valid logic high or low level. To ensure defined outputs from the register before

a stable clock has been supplied, RESET must be held in the low state during power up. In the DDR2 RDIMM

application, RESET is specified to be completely asynchronous with respect to CK and CK. Therefore, no timing

relationship can be ensured between the two. When entering reset, the register will be cleared and the data outputs

will be driven low quickly, relative to the time to disable the differential input receivers. However, when coming out of

reset, the register will become active quickly, relative to the time to enable the differential input receivers. As long as

the data inputs are low, and the clock is stable during the time from the low-to-high transition of RESET until the input

receivers are fully enabled, the design of the ICSSSTUB32S868D must ensure that the outputs will remain low, thus

ensuring no glitches on the output.

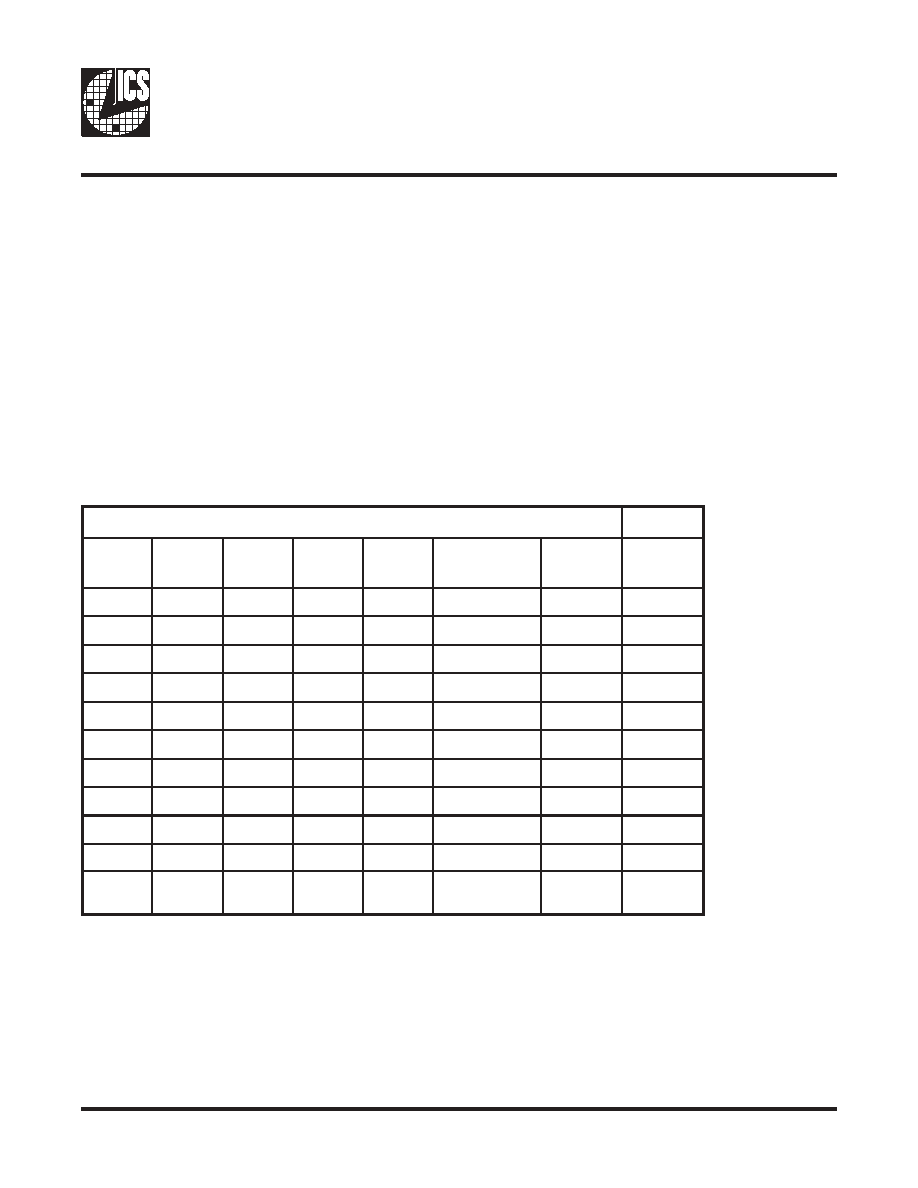

Inpu ts

Output

RST#

DCS0#

DCS1#

CK

CK#

Σ of inputs = H

(D1 - D28)

PAR_I N

QERR#

H

LX

Even

L

H

LX

Odd

L

HLX

Even

H

L

H

LX

Odd

H

XL

Even

L

H

X

L

Odd

L

H

XL

Even

H

L

H

XL

Odd

H

HH

XX

QERR#0 §

HX

X

L or H

X

QERR#0

L

X or

floating

X or

floating

X or

floating

X or

floating

X

X or

floating

H

↑

↓

PAR_IN arrives one clock cycle after the data to which it applies.

This transition assumes QERR# is high at the crossing of CK going high and CK#

going low. If QERR# is low, it stays latches low for two clock cycles or until RST#

is driven low.

§ If DCS0#, DCS1#, and CSGEN are driven high, the device is placed in low-power mode

(LPM). If a parity error occurs on the clock cycle before the device enters the LPM and the

QERR# output is driven low, it stays latches low for the LPM duration plus two clock cycles

or until RST# is driven low.

相关PDF资料 |

PDF描述 |

|---|---|

| MS3106F24-6S | CONN PLUG 8POS STRAIGHT W/SCKT |

| D38999/24FJ61SB | CONN RCPT 61POS JAM NUT W/SCKT |

| MS27499E24A35SB | CONN RCPT 128POS BOX MNT W/SCKT |

| MS27473E18B66SD | CONN PLUG 66POS STRAIGHT W/SCKT |

| MS27473E18B66SC | CONN PLUG 66POS STRAIGHT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SSTUB32S868DHLFT | 功能描述:IC REGIST BUFF 25BIT DDR2 176BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| SSTUB32S869BHLF | 功能描述:IC REGIST BUFF 14BIT DDR2 150BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 信号缓冲器,中继器,分配器 系列:- 标准包装:160 系列:- 类型:转发器 Tx/Rx类型:以太网 延迟时间:- 电容 - 输入:- 电源电压:2.37 V ~ 2.63 V 电流 - 电源:60mA 安装类型:表面贴装 封装/外壳:64-TQFP 裸露焊盘 供应商设备封装:64-TQFP-EP(10x10) 包装:托盘 其它名称:Q5134101 |

| SSTUB32S869BHLFT | 功能描述:IC REGIST BUFF 14BIT DDR2 150BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 信号缓冲器,中继器,分配器 系列:- 标准包装:160 系列:- 类型:转发器 Tx/Rx类型:以太网 延迟时间:- 电容 - 输入:- 电源电压:2.37 V ~ 2.63 V 电流 - 电源:60mA 安装类型:表面贴装 封装/外壳:64-TQFP 裸露焊盘 供应商设备封装:64-TQFP-EP(10x10) 包装:托盘 其它名称:Q5134101 |

| SSTUBF32866AHLF | 制造商:Integrated Device Technology Inc 功能描述:REGISTERED BFFR SGL 25-CH CMOS 96CABGA - Trays |

| SSTUBF32866AHLFT | 制造商:Integrated Device Technology Inc 功能描述:REGISTERED BFFR SGL 25-CH CMOS 96LFBGA - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。