- 您现在的位置:买卖IC网 > PDF目录299933 > ST24C04R (意法半导体) Serial 4K (512 x 8) EEPROM(串行4K EEPROM) PDF资料下载

参数资料

| 型号: | ST24C04R |

| 厂商: | 意法半导体 |

| 英文描述: | Serial 4K (512 x 8) EEPROM(串行4K EEPROM) |

| 中文描述: | 串行4K的(512 × 8)的EEPROM(4K的串行EEPROM中) |

| 文件页数: | 11/16页 |

| 文件大小: | 163K |

| 代理商: | ST24C04R |

AI01100

VCC

CBUS

SDA

RL

MASTER

RL

SCL

CBUS

100

200

300

400

0

4

8

12

16

20

CBUS (pF)

R

L

max

(k

)

VCC = 5V

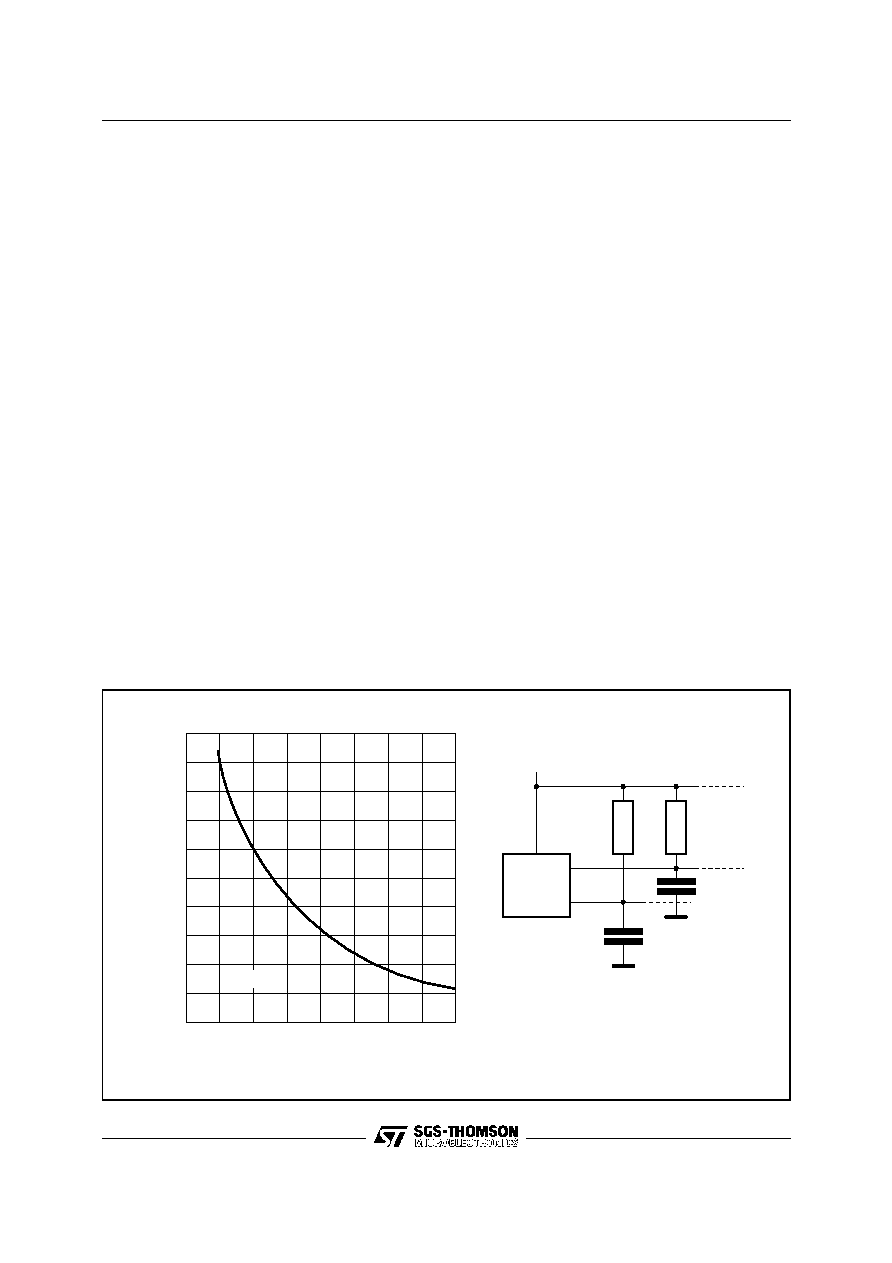

Figure 3. Maximum RL Value versus Bus Capacitance (CBUS) for an I2C Bus

The devices with this Write Control feature no

longer support the Multibyte Write mode of opera-

tion, however all other write modes are fully sup-

ported.

Refer to the AN404 Application Note for more de-

tailed information about Write Control feature.

DEVICE OPERATION

I2C Bus Background

The ST24/25x04 support the I2C protocol. This

protocol defines any device that sends data onto

the bus as a transmitter and any device that reads

the data as a receiver. The device that controls the

data transfer is known as the master and the other

as the slave. The master will always initiate a data

transfer and will provide the serial clock for syn-

chronisation. The ST24/25x04 are always slave

devices in all communications.

Start Condition. START is identified by a high to

low transition of the SDA line while the clock SCL

is stable in the high state. A START condition must

precede any command for data transfer. Except

during a programming cycle, the ST24/25x04 con-

tinuously monitor the SDA and SCL signals for a

START condition and will not respond unless one

is given.

Stop Condition. STOP is identified by a low to high

transition of the SDA line while the clock SCL is

stable in the high state. A STOP condition termi-

nates communication between the ST24/25x04

and the bus master. A STOP condition at the end

of a Read command, after and only after a No

Acknowledge, forces the standby state. A STOP

condition at the end of a Write command triggers

the internal EEPROM write cycle.

Acknowledge Bit (ACK). An acknowledge signal

is used to indicate a successfull data transfer. The

bus transmitter, either master or slave, will release

the SDA bus after sending 8 bits of data. During the

9th clock pulse period the receiver pulls the SDA

bus low to acknowledge the receipt of the 8 bits of

data.

Data Input. During data input the ST24/25x04

sample the SDA bus signal on the rising edge of

the clock SCL. Note that for correct device opera-

tion the SDA signal must be stable during the clock

low to high transition and the data must change

ONLY when the SCL line is low.

Memory Addressing. To start communication be-

tween the bus master and the slave ST24/25x04,

the master must initiate a START condition. Follow-

ing this, the master sends onto the SDA bus line 8

bits (MSB first) corresponding to the device select

code (7 bits) and a READ or WRITE bit.

SIGNAL DESCRIPTIONS (cont’d)

4/16

ST24/25C04, ST24C04R, ST24/25W04

相关PDF资料 |

PDF描述 |

|---|---|

| ST25C08M1 | 1K X 8 SPI BUS SERIAL EEPROM, PDSO8 |

| ST280C04C1L | 960 A, 400 V, SCR, TO-200AB |

| ST280C04C2L | 960 A, 400 V, SCR, TO-200AB |

| ST280C04C2 | 960 A, 400 V, SCR, TO-200AB |

| ST280C04C3L | 960 A, 400 V, SCR, TO-200AB |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST24C04RB1 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM |

| ST24C04RB3 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM |

| ST24C04RB5 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM |

| ST24C04RB6 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM |

| ST24C04RM1 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM |

发布紧急采购,3分钟左右您将得到回复。