- 您现在的位置:买卖IC网 > PDF目录98144 > ST72121J4T1/XXX (STMICROELECTRONICS) 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | ST72121J4T1/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| 封装: | PLASTIC, TQFP-44 |

| 文件页数: | 24/87页 |

| 文件大小: | 1365K |

| 代理商: | ST72121J4T1/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页

30/87

ST72121

WATCHDOG TIMER (Cont’d)

4.2.3 Functional Description

The counter value stored in the CR register (bits

T6:T0), is decremented every 12,288 machine cy-

cles, and the length of the timeout period can be

programmed by the user in 64 increments.

If the watchdog is activated (the WDGA bit is set)

and when the 7-bit timer (bits T6:T0) rolls over

from 40h to 3Fh (T6 becomes cleared), it initiates

a reset cycle pulling low the reset pin for typically

500ns.

The application program must write in the CR reg-

ister at regular intervals during normal operation to

prevent an MCU reset. The value to be stored in

the CR register must be between FFh and C0h

(see Table 12):

– The WDGA bit is set (watchdog enabled)

– The T6 bit is set to prevent generating an imme-

diate reset

– The T5:T0 bits contain the number of increments

which represents the time delay before the

watchdog produces a reset.

Table 12. Watchdog Timing (fCPU =8MHz)

Notes: Following a reset, the watchdog is disa-

bled. Once activated it cannot be disabled, except

by a reset.

The T6 bit canbeused togeneratea softwarere-

set (the WDGA bit is set and the T6 bit is cleared).

If the watchdog is activated, the HALT instruction

will generate a Reset.

4.2.4 Hardware Watchdog Option

If Hardware Watchdog Is selected by option byte,

the watchdog is always active and the WDGA bit in

the CR is not used.

Refer to the device-specific Option Byte descrip-

tion.

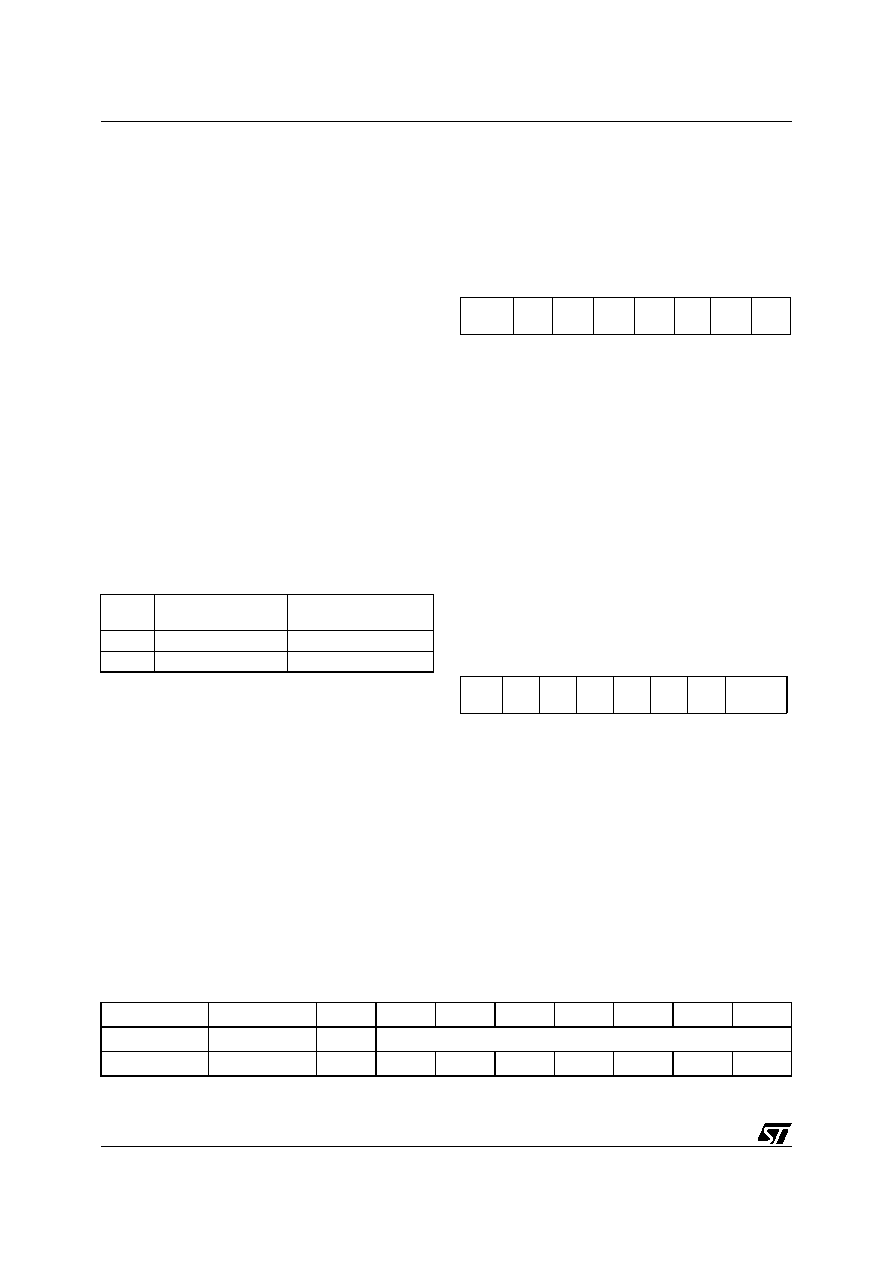

4.2.5 Register Description

CONTROL REGISTER (CR)

Read/Write

Reset Value: 0111 1111 (7Fh)

Bit 7 = WDGA

Activation bit.

This bit is set by software and only cleared by

hardware after a reset. When WDGA = 1, the

watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

Note: This bit is not used if the hardware watch-

dog otion is enabled by option byte.

Bit 6-0 = T[6:0]

7-bit timer (MSB to LSB).

These bits contain the decremented value. A reset

is produced when it rolls over from 40h to 3Fh (T6

become cleared).

STATUS REGISTER (SR)

Read/Write

Reset Value*: 0000 0000 (00h)

Bit 0 = WDOGF

Watchdog flag.

This bit is set by a watchdog reset and cleared by

software or a power on/off reset. This bit is useful

for distinguishing power/on off or external reset

and watchdog reset.

0: No Watchdog reset occurred

1: Watchdog reset occurred

* Only by software and power on/off reset

Note: This register is not used in versions without

LVD Reset.

Table 13. WDG Register Map

CR Register

initial value

WDG timeout period

(ms)

Max

FFh

98.304

Min

C0h

1.536

70

WDGA

T6

T5

T4

T3

T2

T1

T0

70

-

---

WDOGF

Address (Hex.)

Register Name

76543

210

2A

CR

WDGA

T6.. T0

2B

SR

-

WDOGF

30

相关PDF资料 |

PDF描述 |

|---|---|

| ST72121J2T3/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP44 |

| ST72121J2T6/XXX | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| ST72141K2B3/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP32 |

| ST72311N4T6/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| ST72311J2B6/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST72124J | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH SINGLE VOLTAGE FLASH MEMORY, ADC, 16-BIT TIMERS, SPI, SCI INTERFACES |

| ST72124J2 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH SINGLE VOLTAGE FLASH MEMORY, ADC, 16-BIT TIMERS, SPI, SCI INTERFACES |

| ST72124J2B | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH SINGLE VOLTAGE FLASH MEMORY, ADC, 16-BIT TIMERS, SPI, SCI INTERFACES |

| ST72124J2B1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH SINGLE VOLTAGE FLASH MEMORY, ADC, 16-BIT TIMERS, SPI, SCI INTERFACES |

| ST72124J2B1/XXX | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT MCU WITH SINGLE VOLTAGE FLASH MEMORY, ADC, 16-BIT TIMERS, SPI, SCI INTERFACES |

发布紧急采购,3分钟左右您将得到回复。