- 您现在的位置:买卖IC网 > PDF目录372330 > STEL-1378A FREQUENCY SYNTHESIZER|HYBRID|DIP|64PIN|PLASTIC PDF资料下载

参数资料

| 型号: | STEL-1378A |

| 英文描述: | FREQUENCY SYNTHESIZER|HYBRID|DIP|64PIN|PLASTIC |

| 中文描述: | 频率合成器|混合|双酯| 64管脚|塑料 |

| 文件页数: | 4/19页 |

| 文件大小: | 284K |

| 代理商: | STEL-1378A |

STEL-2060C

4

INPUT SIGNALS

RESET

Reset

. A logic low on this asynchronous input will completely

reset all registers in the decoder to an initial condition within

20 nsec. Normal operation will commence after

RESET

goes

high. This will not affect the values stored in the decision

path memory but will reset the node sync state to the initial

condition.

DCLKIN

D

ecoder

cl

oc

k in

put. It is the reference clock for all internal

synchronous functions in the decoder when operating in the

Internal Puncturing mode. It should nominally be a square

wave with a maximum frequency of 45 MHz, corresponding

to a decoded data rate of 45 Mbps. When operating at Rate

1

/

2

and in the External Puncturing mode this clock will be

generated internally from

SYMCKIN

,

and

DCLKIN

should

be connected to ground.

SYMCKIN

Sym

bol

c

loc

k in

put. This is the reference clock for all

internal synchronous functions in the symbol alignment and

depuncturing circuits. It should nominally be a square wave

with a maximum frequency of 90 MHz. Its frequency should

be equal to f

DCLKIN

/2R in the parallel input mode

(

PARL

= 1) and equal to f

DCLKIN

/R in the sequential input

mode (

PARL

= 0), where R is the decoding rate when using

internal depuncturing. Please refer to the section on

Punctured Mode Operation for more detailed information.

G1

2-0

, G2

2-0

The

G1

2-0

and

G2

2-0

signals are the 3-bit soft decision input

symbols to the decoder. They are presented to the decoder

either sequentially or in parallel depending on the states of

the

PARL

and

RATE

2-0

inputs. In the parallel mode

(

PARL

= 1) the symbols are clocked into the device on the

rising edges of

SYMCKIN

when

RATE

2-0

= 0 (Rate

1

/

2

and

External Depuncturing) and on both edges of

SYMCKIN

when

RATE

2-0

≠

0 (Internal Depuncturing). In the sequential

mode (

PARL

= 0) in which the

G2

2-0

inputs are not used, both

the G1 and G2 symbols are loaded via the

G1

2-0

pins. The G1

symbols are then latched in on the rising edges of

SYMCKIN

when

LDG2

is low and the G2 symbols are latched in on the

rising edges of

SYMCKIN

when

LDG2

is high.

LDG2

When this signal is high during a rising edge of

SYMCKIN

the symbol loaded into the

G1

2-0

pins will be G2. This

function is only active when

PARL

is set low (sequential

input mode) and

RATE

2-0

is set to 000 (Rate

1

/

2

operation or

External Puncturing mode). If auto node sync is used, the

LDG2

signal can be derived by dividing the

SYMCKIN

signal by two. The auto node sync will then compensate for

the phase ambiguity.

PARL

When this signal is high, the input symbols are accepted in

par

alle

l

by the chip, using the

G1

2-0

pins for the G1 symbols

and the

G2

2-0

pins for the G2 symbols. When it is set low, the

inputs are accepted sequentially, using the

G1

2-0

pins for

both symbols. The sequential input is most suited for BPSK

data, and the parallel input is most suited for QPSK data. The

auto node sync sequence will operate on the assumption that

the signal is BPSK modulated when

PARL

is set low and

QPSK modulated when it is set high. Setting

PARL

low adds

two cycles of

ODCLK

to the pipeline delay.

OBIN

The STEL-2060CCC can accept the soft-decision input data

in either

o

ffset

bin

ary or offset signed-magnitude formats.

When the

OBIN

input is set high, the format expected will be

offset binary; when it is set low it will be offset signed-

magnitude. The meanings of the 3-bit values for these two

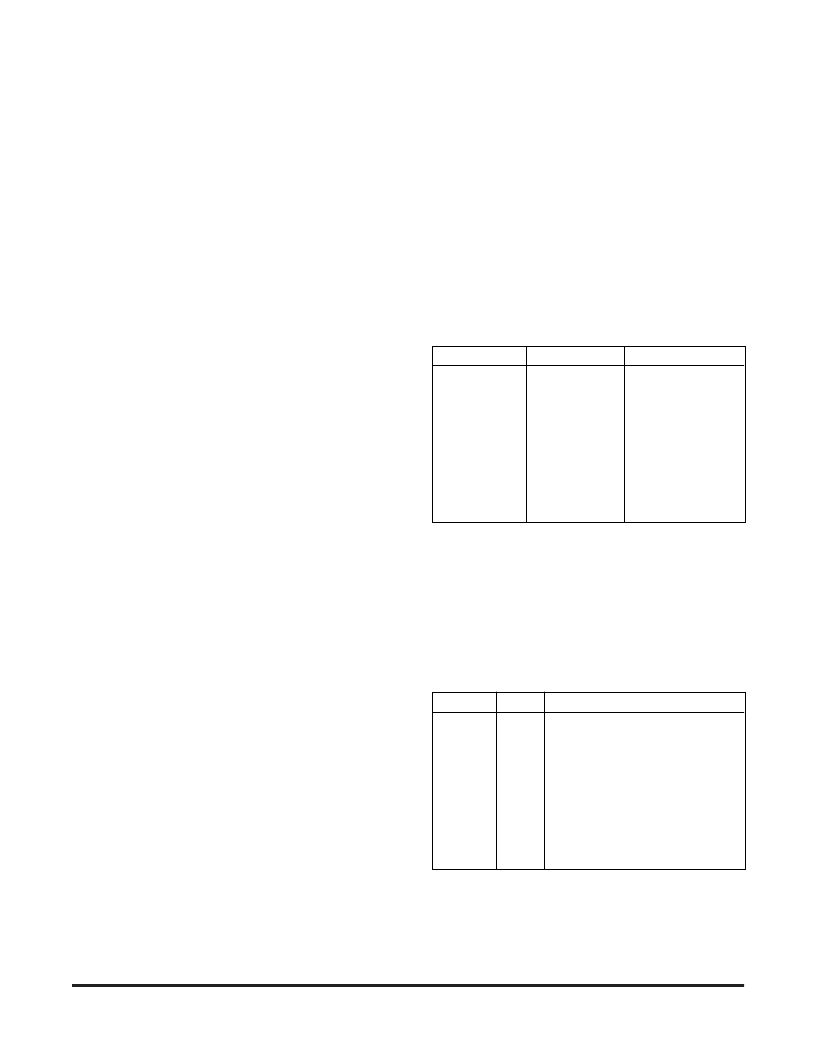

codes is shown in the following table:

OBIN

= 1

OBIN

= 0

Value

111

110

101

100

011

010

001

000

111

110

101

100

000

001

010

011

Most confident +

(Data = 1)

Least confident +

Least confident –

(Data = 0)

Most confident –

When using the STEL-2060CCC with hard-decision data, the

symbols should be loaded into the

G1

2

and

G2

2

pins. The

other symbol inputs should be set to a logic high level and

OBIN

should be set low.

RATE

2-0

These signals select the decoding rate for unpunctured

operation (Rate

1

/

2

) and internally supported depuncturing

patterns (Rates

2

/

3

,

3

/

4

and

7

/

8

). These patterns are shown

in the following table, where a 0 in the pattern indicates a

punctured symbol:

RATE

2-0

Rate

Pattern

0 0 0

0 0 1

1

/

2

2

/

3

N.A.

G1:

G2:

10

11

1 0 0

3

/

4

G1:

G2:

101

110

0 1 0

7

/

8

G1:

G2:

1000101

1111010

Other puncturing patterns can be implemented externally

using the

PNCG1

and

PNCG2

inputs.

DDIF

When this input is set high, it causes the data out of the

Viterbi

d

ecoder to be

dif

ferentially decoded. This adds one

cycle of

ODCLK

to the pipeline delay.

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相关PDF资料 |

PDF描述 |

|---|---|

| STEPHY1 | Semiconductor Fuse; Current Rating:35A; Voltage Rating:250V; Fuse Type:Fast Acting; Fuse Terminals:Blade; Diameter:20.6mm; Length:81mm; Series:L25S; Voltage Rating:250V |

| STF201-22.TC | Semiconductor Fuse; Current Rating:50A; Voltage Rating:250V; Fuse Type:Fast Acting; Fuse Terminals:Blade; Diameter:20.6mm; Length:81mm; Series:L25S; Voltage Rating:250V |

| STF201-30.TC | Triac; Thyristor Type:Sensitive Gate; Peak Repetitive Off-State Voltage, Vdrm:200V; On-State RMS Current, IT(rms):800mA; Gate Trigger Current (QI), Igt:5mA; Current, It av:0.8A; Leaded Process Compatible:Yes RoHS Compliant: Yes |

| STF203-15.TC | Analog Miscellaneous |

| STF203-22.TC | SUPPRESSOR CIRCUIT|TSSOP|6PIN|PLASTIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| STEL-2000A+20/CR | 制造商:未知厂家 制造商全称:未知厂家 功能描述:RF MODULATOR/DEMODULATOR|CMOS|QFP|100PIN|PLASTIC |

| STEL-2000A+45/CR | 制造商:未知厂家 制造商全称:未知厂家 功能描述:RF MODULATOR/DEMODULATOR|CMOS|QFP|100PIN|PLASTIC |

| STEL2020 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Convolutional-FEC-Viterbi Error Circuit - Burst and continuous modes |

| STEL-2020 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Convolutional-FEC-Viterbi Error Circuit - Burst and continuous modes |

| STEL-2030B/CM | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Error Correction for Telecom |

发布紧急采购,3分钟左右您将得到回复。