- 您现在的位置:买卖IC网 > PDF目录98149 > SX28AC/SSU 2 CHANNEL(S), I2C BUS CONTROLLER, PDSO28 PDF资料下载

参数资料

| 型号: | SX28AC/SSU |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), I2C BUS CONTROLLER, PDSO28 |

| 封装: | GREEN, PLASTIC, SSOP-28 |

| 文件页数: | 17/48页 |

| 文件大小: | 772K |

| 代理商: | SX28AC/SSU |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

2005 Ubicom, Inc. All rights reserved.

- 24 -

www.ubicom.com

SX20AC/SX28AC

10.2 Watchdog Timer

The watchdog logic consists of a Watchdog Timer which

shares the same 8-bit programmable prescaler with the

RTCC. The prescaler actually serves as a postscaler if

used in conjunction with the WDT, in contrast to its use as

a prescaler with the RTCC. The WDT is clocked by it’s

own internal RC oscillator.

The Watchdog oscillator has a nominal operating fre-

quency of 16 kHz, or a period of 62.5 microseconds. At

this rate, the 8-bit counter counts from 00h to FFh in 16

milliseconds. In the default configuration (prescaler

assigned to WDT, with divide rate set to 1:128), the appli-

cation program needs to execute a “CLR !WDT” instruc-

tion at least once every 2 seconds to prevent a Watchdog

reset (if the WDTE bit in the FUSE register is set to 1).

See Table 4-2.

10.3 The Prescaler

The 8-bit prescaler may be assigned to either the RTCC

or the WDT through the PSA bit (bit 3 of the OPTION reg-

ister). Setting the PSA bit assigns the prescaler to the

WDT. If assigned to the WDT, the WDT clocks the pres-

caler and the prescaler divide rate is selected by the

PS0, PS1, and PS2 bits located in the OPTION register.

Clearing the PSA bit assigns the prescaler to the RTCC.

Once assigned to the RTCC, the prescaler clocks the

RTCC and the divide rate is selected by the PS0, PS1,

and PS2 bits in the OPTION register. The prescaler is not

mapped into the data memory, so run-time access is not

possible.

The prescaler cannot be assigned to both the RTCC and

WDT simultaneously.

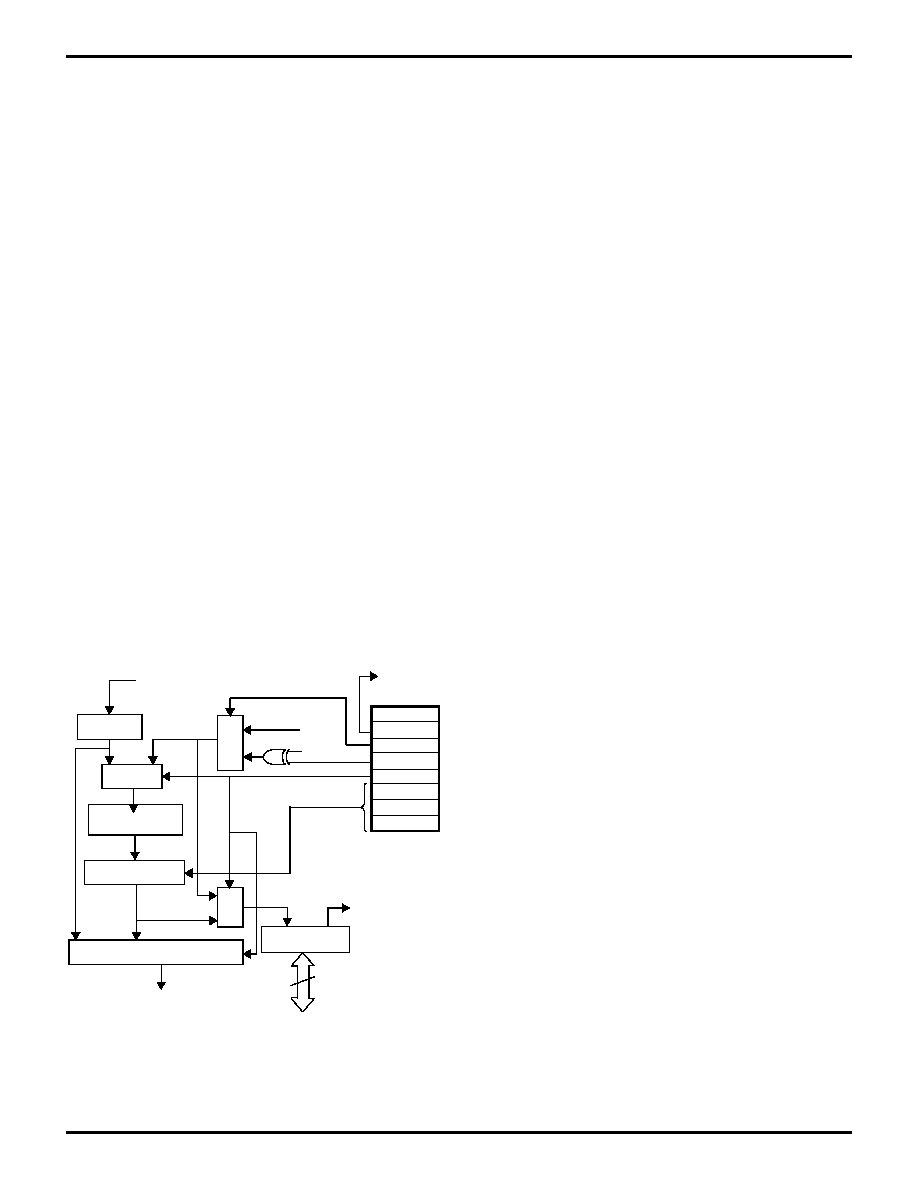

Figure 10-1. RTCC and WDT Block Diagram

WDTE (from FUSE Word)

RTCC pin

MUX

8-Bit Prescaler

MUX (8 to 1)

8-Bits

WDT Time-out

Data Bus

WDT

MUX

M

RTCC

M

U

X

FOSC

RST

RTE_ES

PSA

PS2

PS1

PS0

OPTION

Register

RTCC Rollover

Interrupt

RTE_IE

RTW

RTCC

Interrupt

Enable

U

X

相关PDF资料 |

PDF描述 |

|---|---|

| SY100EP11UZITR | 100E SERIES, LOW SKEW CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| SY100EP195VTCTR | ACTIVE DELAY LINE, COMPLEMENTARY OUTPUT, PQFP32 |

| SY100EP195VTG | ACTIVE DELAY LINE, COMPLEMENTARY OUTPUT, PQFP32 |

| SY100EP196VTCTR | ACTIVE DELAY LINE, COMPLEMENTARY OUTPUT, PQFP32 |

| SY100EP196VTC | ACTIVE DELAY LINE, COMPLEMENTARY OUTPUT, PQFP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SX28AD100-I/DP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configurable Communications Controllers with EE/Flash Program Memory, In-System Programming Capability and On-Chip Debug |

| SX28AD100-I/PQ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configurable Communications Controllers with EE/Flash Program Memory, In-System Programming Capability and On-Chip Debug |

| SX28AD100-I/SO | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configurable Communications Controllers with EE/Flash Program Memory, In-System Programming Capability and On-Chip Debug |

| SX28AD100-I/SS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configurable Communications Controllers with EE/Flash Program Memory, In-System Programming Capability and On-Chip Debug |

| SX28AD100-I/TQ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Configurable Communications Controllers with EE/Flash Program Memory, In-System Programming Capability and On-Chip Debug |

发布紧急采购,3分钟左右您将得到回复。