- 您现在的位置:买卖IC网 > PDF目录98179 > TC7135CPI 1-CH 9-BIT DUAL-SLOPE ADC, PARALLEL ACCESS, PDIP28 PDF资料下载

参数资料

| 型号: | TC7135CPI |

| 元件分类: | ADC |

| 英文描述: | 1-CH 9-BIT DUAL-SLOPE ADC, PARALLEL ACCESS, PDIP28 |

| 封装: | PLASTIC, DIP-28 |

| 文件页数: | 2/16页 |

| 文件大小: | 217K |

| 代理商: | TC7135CPI |

10

TC7135

4-1/2 DIGIT

ANALOG-TO-DIGITAL CONVERTER

TC7135-10 9/27/99

High-Speed Operation

The maximum conversion rate of most dual-slope ADCs

is limited by frequency response of the comparator. The

comparator in this circuit follows the integrator ramp with a

3

s delay, and at a clock frequency of 160kHz (6s period),

half of the first reference integrate clock period is lost in

delay. This means the meter reading will change from 0 to

1 with a 50

V input, 1 to 2 with 150V, 2 to 3 with 250V, etc.

This transition at midpoint is considered desirable by most

users; however, if clock frequency is increased appreciably

above 160kHz, the instrument will flash "1" on noise peaks

even when the input is shorted.

For many dedicated applications, where the input signal

is always of one polarity, comparator delay need not be a

limitation. Since nonlinearity and noise do not increase

substantially with frequency, clock rates up to ~1MHz may

be used. For a fixed clock frequency, the extra count (or

counts) caused by comparator delay will be constant and

can be digitally subtracted.

The clock frequency may be extended above 160kHz

without this error, however, by using a low value resistor in

series with the integrating capacitor. The effect of the

resistor is to introduce a small pedestal voltage onto the

integrator output at the beginning of reference-integrate

phase. By careful selection of the ratio between this resis-

tor and the integrating resistor (a few tens of ohms in the

recommended circuit), the comparator delay can be com-

pensated for and maximum clock frequency extended

by approximately a factor of 3. At higher frequencies, ring-

ing and second-order breaks will cause significant

nonlinearities during the first few counts of the instrument.

The minimum clock frequency is established by leakage

on the auto-zero and reference capacitors. With most de-

vices, measurement cycles as long as 10 seconds give no

measurable leakage error.

The clock used should be free from significant phase or

frequency jitter. Several suitable low-cost oscillators are

shown in the applications section. The multiplexed output

means if the display takes significant current from the logic

supply, the clock should have good PSRR.

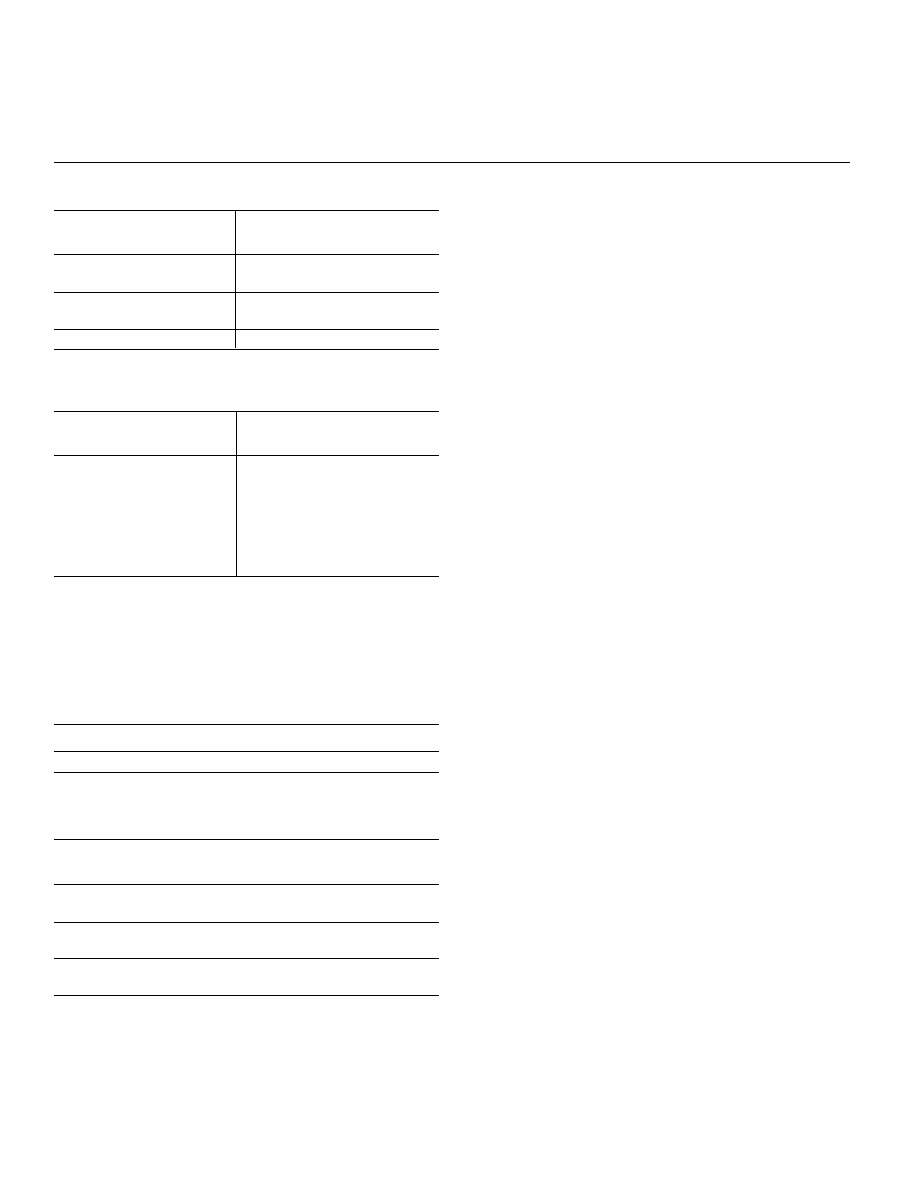

Table 3. Conversion Rate vs. Clock Frequency

Conversion Rate

Clock

(Conv/Sec)

Frequency (kHz)

2.5

100

3.0

120

5.0

200

7.5

300

10.0

400

20.0

800

30.0

1200

Displays and Driver Circuits

TelCom Semiconductor manufactures three display de-

coder/driver circuits to interface the TC7135 to LCDs or LED

displays. Each driver has 28 outputs for driving four 7-

segment digit displays.

Device

Package

Description

TC7211AIPL

40-Pin Epoxy

4-Digit LCD Driver/Encoder

Several sources exist for LCDs and LED displays.

Display

Manufacturer

Address

Type

Hewlett Packard

640 Page Mill Road

LED

Components

Palo Alto, CA 94304

AND

720 Palomar Ave.

LCD and

Sunnyvale, CA 94086

LED

Epson America, Inc.

3415 Kanhi Kawa St.

LCD

Torrance, CA 90505

Table 2. Line Frequency Rejection

Oscillator Frequency

Frequency Rejected

(kHz)

(Hz)

300, 200, 150, 120,

60

100, 40, 33-1/3

250, 166-2/3,

50

125, 100

100

50, 60, 400

相关PDF资料 |

PDF描述 |

|---|---|

| TC7135CBURT | 1-CH DUAL-SLOPE ADC, ACCESS, PQFP64 |

| TC7135CLI | 1-CH DUAL-SLOPE ADC, PQCC28 |

| TC7135CBUTR | 1-CH DUAL-SLOPE ADC, PQFP64 |

| TC7135CKW | 1-CH DUAL-SLOPE ADC, PQFP64 |

| TC7135CLITR | 1-CH DUAL-SLOPE ADC, PQCC28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TC7135CPL | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:4-1/2 Digit A/D Converter |

| TC7136 | 制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Low Power 3-1/2 Digit Analog-to-Digital Converter |

| TC7136A | 制造商:TELCOM 制造商全称:TelCom Semiconductor, Inc 功能描述:LOW POWER, 3-1/2 DIGIT ANALOG-TO-DIGITAL CONVERTERS |

| TC7136ACKW | 功能描述:LCD 驱动器 Low Power RoHS:否 制造商:Maxim Integrated 数位数量:4.5 片段数量:30 最大时钟频率:19 KHz 工作电源电压:3 V to 3.6 V 最大工作温度:+ 85 C 最小工作温度:- 20 C 封装 / 箱体:PDIP-40 封装:Tube |

| TC7136ACKW713 | 功能描述:LCD 驱动器 Low Power RoHS:否 制造商:Maxim Integrated 数位数量:4.5 片段数量:30 最大时钟频率:19 KHz 工作电源电压:3 V to 3.6 V 最大工作温度:+ 85 C 最小工作温度:- 20 C 封装 / 箱体:PDIP-40 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。