- 您现在的位置:买卖IC网 > PDF目录98219 > THS1240IPHP (TEXAS INSTRUMENTS INC) 1-CH 12-BIT DELTA-SIGMA ADC, PARALLEL ACCESS, PQFP48 PDF资料下载

参数资料

| 型号: | THS1240IPHP |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 1-CH 12-BIT DELTA-SIGMA ADC, PARALLEL ACCESS, PQFP48 |

| 封装: | POWER, PLASTIC, TQFP-48 |

| 文件页数: | 19/20页 |

| 文件大小: | 450K |

| 代理商: | THS1240IPHP |

THS1240

12-BIT 40 MSPS IF SAMPLING COMMUNICATIONS

ANALOG-TO-DIGITAL CONVERTER

SLAS279D – JUNE 2000 – REVISED JANUARY 2001

8

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

APPLICATION INFORMATION

using the THS1240 references

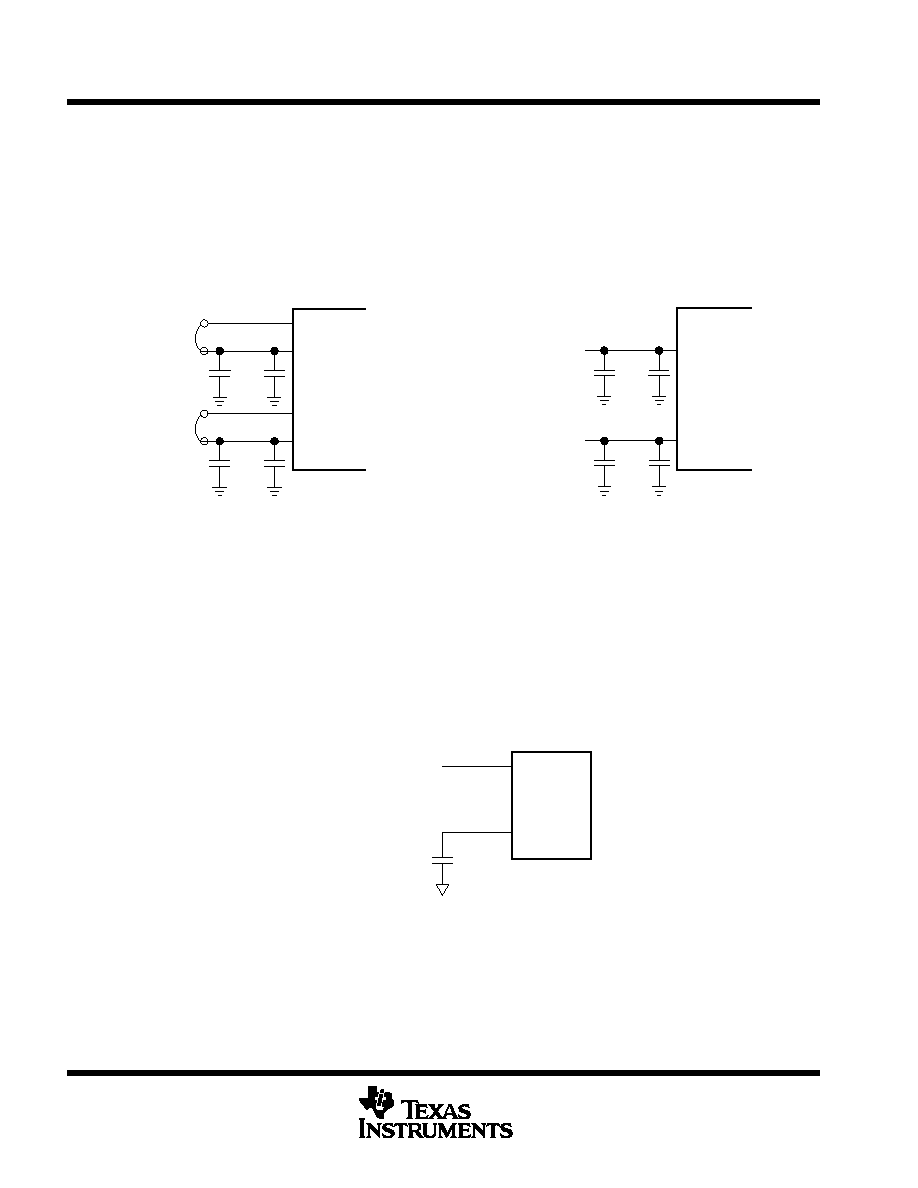

The option of internal or external reference is provided by allowing for an external connection of the internal

reference to the reference inputs. This type of reference selection offers the lowest noise possible by not relying

on any active switch to make the selection. Compensating each reference output with a 1-

F and 0.01-F chip

capacitor is required as shown in Figure 6. The differential analog input range is equal to 2 (VREFOUT+ –

VREFOUT–). When using external references, it is best to decouple the reference inputs with a 0.1-F and

0.01-

F chip capacitor as shown in Figure 7.

0.01

F

1

F

0.01

F

1

F

VREFIN+

VREFOUT+

VREFIN–

VREFOUT–

Figure 6. Internal Reference Usage

Figure 7. External Reference Usage

0.01

F

0.1

F

0.01

F

0.1

F

External Reference +

VREFIN+

VREFIN–

External Reference –

using the THS1240 clock input

The THS1240 clock input can be driven with either a differential clock signal or a single ended clock input with

little or no difference in performance between the single-ended and differential-input configurations. The

common mode of the clock inputs is set internally to VDD/2 using 5-k resistors (Figure 4).

The THS1240 clock input requires a common mode voltage or dc component of VDD/2. It is possible for the

common mode voltage of the clock source to differ from VDD/2 by as much as 10% with little or no performance

degradation. The clock input should be either a sinewave or a square wave having a 50% duty cycle.

When driven with a single-ended CMOS clock input, it is best to connect the CLK– input to ground with a 0.01

F

capacitor (see Figure 8).

CLK+

THS1240

CLK–

Square Wave or Sine Wave

2 V p-p to 5 V p-p

Common Mode Voltage = VDD/2

0.01

F

Figure 8. Driving the Clock From a Single-Ended Clock Source

相关PDF资料 |

PDF描述 |

|---|---|

| THS1240CPHP | 1-CH 12-BIT DELTA-SIGMA ADC, PARALLEL ACCESS, PQFP48 |

| THS1240I | 1-CH 12-BIT DELTA-SIGMA ADC, PARALLEL ACCESS, PQFP48 |

| THS1240C | 1-CH 12-BIT DELTA-SIGMA ADC, PARALLEL ACCESS, PQFP48 |

| THS1401QPFB | 1-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| THS1403QPFB | 1-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| THS125 | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:HIGH STABILITY MOTOR CONTROL. DIGITAL TACHOMETER. CRANK SHAFT POSITION SENSOR. |

| THS126 | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:HIGH STABILITY MOTOR CONTROL. DIGITAL TACHOMETER. CRANK SHAFT POSITION SENSOR. |

| THS126(F) | 制造商:Toshiba 功能描述:Cut Tape |

| THS128 | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:HIGH STABILITY MOTOR CONTROL. DIGITAL TACHOMETER. |

| THS129 | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:HIGH STABILITY MOTOR CONTROL. DIGITAL TACHOMETER. |

发布紧急采购,3分钟左右您将得到回复。