- 您现在的位置:买卖IC网 > PDF目录67341 > TLV1548CDBRG4 (TEXAS INSTRUMENTS INC) 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 PDF资料下载

参数资料

| 型号: | TLV1548CDBRG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| 封装: | GREEN, PLASTIC, SSOP-20 |

| 文件页数: | 37/37页 |

| 文件大小: | 693K |

| 代理商: | TLV1548CDBRG4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

9

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

extended sampling, asynchronous start of sampling: CSTART operation

The extended sampling mode of operation programs the acquisition time (tACQ) of the sample-and-hold circuit.

This allows the analog inputs of the device to be directly interfaced to a wide range of input source impedances.

The extended sampling mode consumes higher power depending on the duration of the sampling period

chosen.

CSTART controls the sampling period and starts the conversion. The falling edge of CSTART initiates the

sampling period of a preset channel. The low time of CSTART controls the acquisition time of the input

sample-and-hold circuit. The sample is held on the rising edge of CSTART. Asserting CSTART causes the

converter to perform a new sample of the signal on the preset valid MUX channel (one of the eight) and discard

the current conversion result ready for output. Sampling continues as long as CSTART is active (negative). The

rising edge of CSTART ends the sampling cycle. The conversion cycle starts two internal system clocks after

the rising edge of CSTART.

Once the conversion is complete, the processor can initiate a normal I/O cycle to read the conversion result and

set the MUX address for the next conversion. Since the internal flag AsyncFlag is set high, this flag setting

indicates the cycle is an output cycle, so no conversion is performed during the cycle. The internal state machine

tests the AsyncFlag on the falling edge of CS. AsyncFlag is set high at the rising edge of CSTART, and it is reset

low at the rising edge of each CS. A conversion cycle follows a sampling cycle only if AsyncFlag is tested as

low at the falling edge of CS. As shown in Figure 2, an asynchronous I/O cycle can be removed by two

consecutive normal I/O cycles.

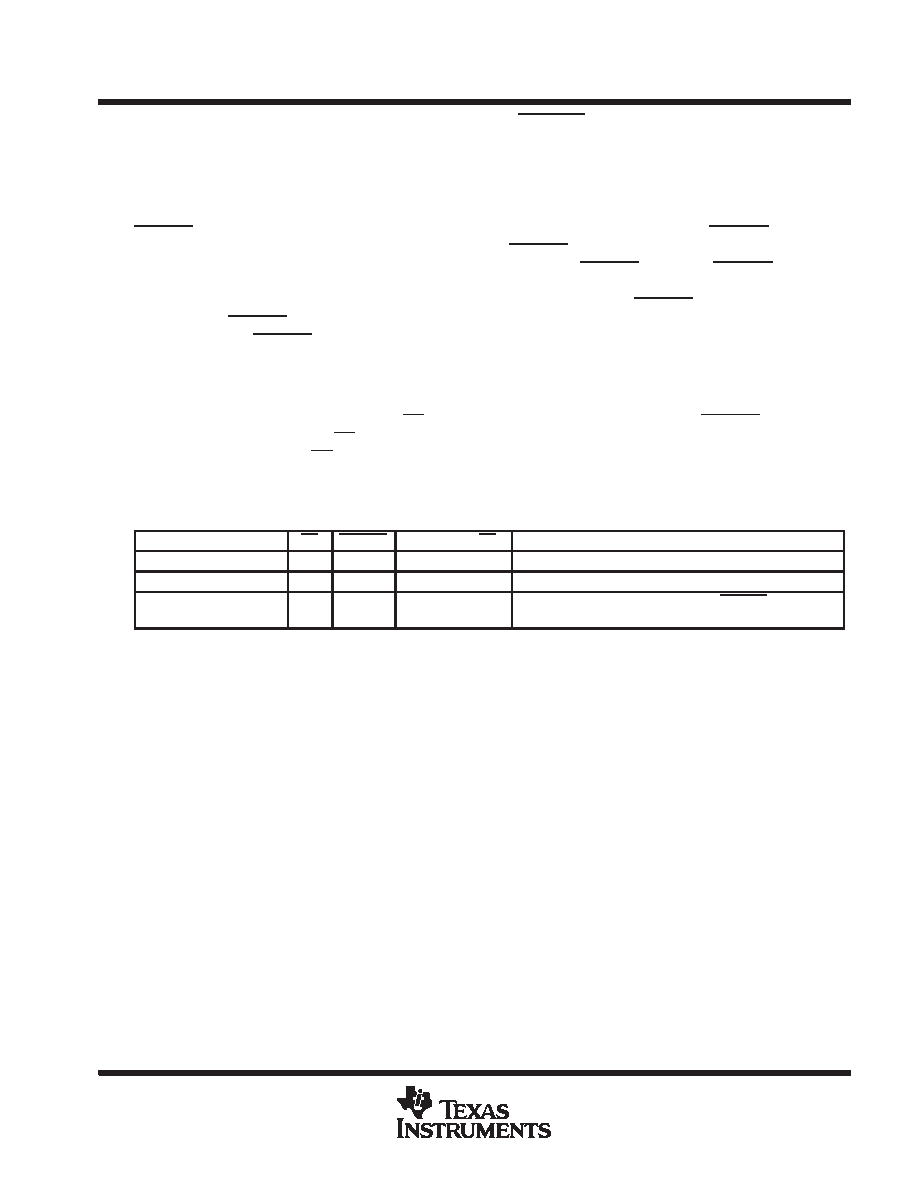

Table 4. TLV1544/1548 Hardware Configuration for Different Operating Modes

OPERATING MODES

CS

CSTART

AsyncFlag at CS

↓

ACTION

Normal sampling

Low

High

Low

Fixed 6 I/O CLK sampling, synchronous conversion follows

Normal I/O (read out only)

Low

High

No sampling, no conversion

Extended sampling

High

Low

N/A

Flexible sampling period controlled by CSTART,

asynchronous conversion follows

相关PDF资料 |

PDF描述 |

|---|---|

| TLV1544IPW | 4-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO16 |

| TLV1544CD | 4-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO16 |

| TLV1544CDR | 4-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO16 |

| TLV1544IDR | 4-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO16 |

| TLV1544CPWR | 4-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TLV1548-EP | 制造商:TI 制造商全称:Texas Instruments 功能描述:LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTER WITH SERIAL CONTROL AND 8 ANALOG INPUTS |

| TLV1548I | 制造商:TI 制造商全称:Texas Instruments 功能描述:LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS |

| TLV1548IDB | 功能描述:模数转换器 - ADC 10bit A/D w/DSP Int RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV1548IDBG4 | 功能描述:模数转换器 - ADC 10-Bit 85 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV1548IDBR | 功能描述:模数转换器 - ADC 10-Bit 85 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。