- 您现在的位置:买卖IC网 > PDF目录98254 > TLV320AIC32IRHBR (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQCC32 PDF资料下载

参数资料

| 型号: | TLV320AIC32IRHBR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC32 |

| 封装: | 5 X 5 MM, GREEN, PLASTIC, QFN-32 |

| 文件页数: | 25/80页 |

| 文件大小: | 1270K |

| 代理商: | TLV320AIC32IRHBR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

DELTA-SIGMA AUDIO DAC

AUDIO DAC DIGITAL VOLUME CONTROL

ANALOG OUTPUT COMMON-MODE ADJUSTMENT

www.ti.com ............................................................................................................................................. SLAS479C – AUGUST 2005 – REVISED DECEMBER 2008

The stereo audio DAC incorporates a third order multi-bit delta-sigma modulator followed by an analog

reconstruction filter. The DAC provides high-resolution, low-noise performance, using oversampling and noise

shaping techniques. The analog reconstruction filter design consists of a 6-tap analog FIR filter followed by a

continuous time RC filter. The analog FIR operates at a rate of 128 × Fsref (6.144 MHz when Fsref = 48 kHz,

5.6448 MHz when Fsref = 44.1 kHz). Note that the DAC analog performance may be degraded by excessive

clock jitter on the MCLK input. Therefore, care must be taken to keep jitter on this clock to a minimum.

The audio DAC includes a digital volume control block which implements a programmable digital gain. The

volume level can be varied from 0 dB to –63.5 dB in 0.5-dB steps, in addition to a mute bit, independently for

each channel. The volume level of both channels can also be changed simultaneously by the master volume

control. Gain changes are implemented with a soft-stepping algorithm, which only changes the actual volume by

one step per input sample, either up or down, until the desired volume is reached. The rate of soft-stepping can

be slowed to one step per two input samples through a register bit.

Because of soft-stepping, the host does not know when the DAC has been actually muted. This may be

important if the host wishes to mute the DAC before making a significant change, such as changing sample

rates. In order to help with this situation, the device provides a flag back to the host via a read-only register bit

that alerts the host when the part has completed the soft-stepping and the actual volume has reached the

desired volume level. The soft-stepping feature can be disabled through register programming. If soft-stepping is

enabled, the MCLK signal should be kept applied to the device until the DAC power-down flag is set. When this

flag is set, the internal soft-stepping process and power down sequence is complete, and the MCLK can then be

stopped if desired.

The TLV320AIC32 also includes functionality to detect when the user switches on or off the de-emphasis or

digital audio processing functions, to first (1) soft-mute the DAC volume control, (2) change the operation of the

digital effects processing, and (3) soft-unmute the part. This avoids any possible pop/clicks in the audio output

due to instantaneous changes in the filtering. A similar algorithm is used when first powering up or down the

DAC. The circuit begins operation at power up with the volume control muted, then soft-steps it up to the desired

volume level. At power down, the logic first soft-steps the volume down to a mute level, then powers down the

circuitry.

The output common-mode voltage and output range of the analog output are determined by an internal bandgap

reference, in contrast to other codecs that may use a divided version of the supply. This scheme is used to

reduce the coupling of noise that may be on the supply (such as 217-Hz noise in a GSM cellphone) into the

audio signal path.

However, due to the possible wide variation in analog supply range (2.7 V – 3.6 V), an output common-mode

voltage setting of 1.35 V, which would be used for a 2.7 V supply case, will be overly conservative if the supply is

actually much larger, such as 3.3 V or 3.6 V. In order to optimize device operation, the TLV320AIC32 includes a

programmable output common-mode level, which can be set by register programming to a level most appropriate

to the actual supply range used by a particular customer. The output common-mode level can be varied among

four different values, ranging from 1.35 V (most appropriate for low supply ranges, near 2.7 V) to 1.8 V (most

appropriate for high supply ranges, near 3.6 V). Note that there is also some limitation on the range of DVDD

voltage as well in determining which setting is most appropriate.

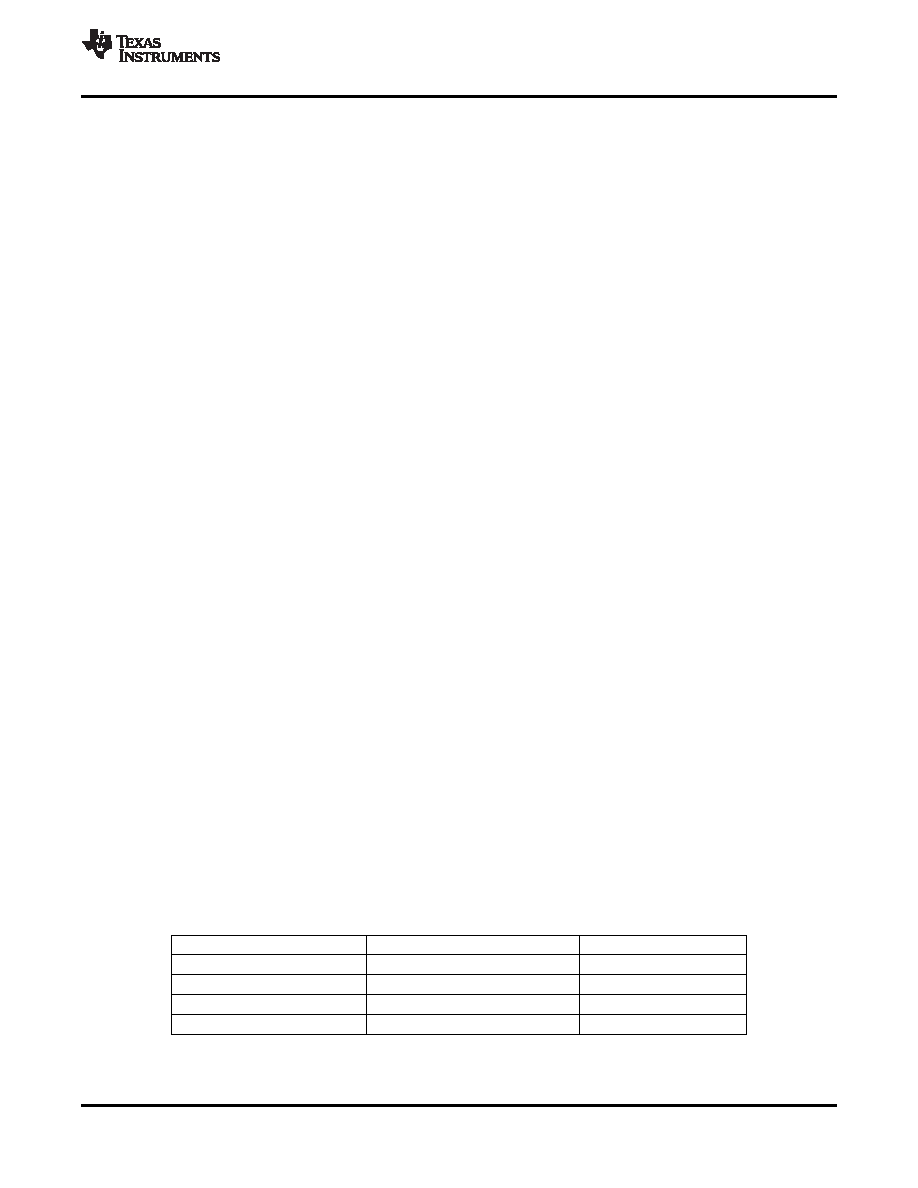

Table 4. Appropriate Settings

CM SETTING

RECOMMENDED AVDD, DRVDD

RECOMMENDED DVDD

1.35

2.7 V – 3.6 V

1.65 V – 1.95 V

1.50

3.0 V – 3.6 V

1.65 V – 1.95 V

1.65 V

3.3 V – 3.6 V

1.8 V – 1.95 V

1.8 V

3.6 V

1.95 V

Copyright 2005–2008, Texas Instruments Incorporated

31

Product Folder Link(s): TLV320AIC32

相关PDF资料 |

PDF描述 |

|---|---|

| TLV320AIC32IRHBRG4 | SPECIALTY CONSUMER CIRCUIT, PQCC32 |

| TLV320AIC32IRHBT | SPECIALTY CONSUMER CIRCUIT, PQCC32 |

| TLV320AIC32IRHBTG4 | SPECIALTY CONSUMER CIRCUIT, PQCC32 |

| TLV320AIC32IRHB | SPECIALTY CONSUMER CIRCUIT, PQCC32 |

| TLV320AIC33IGQER | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TLV320AIC32IRHBRG4 | 功能描述:接口—CODEC Lo-Pwr Stereo Codec w/6 Inp 6 Otp RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| TLV320AIC32IRHBT | 功能描述:接口—CODEC Lo-Pwr Stereo Codec w/6 Inp 6 Otp RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| TLV320AIC32IRHBTG4 | 功能描述:接口—CODEC Lo-Pwr Stereo Codec w/6 Inp 6 Otp RoHS:否 制造商:Texas Instruments 类型: 分辨率: 转换速率:48 kSPs 接口类型:I2C ADC 数量:2 DAC 数量:4 工作电源电压:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:DSBGA-81 封装:Reel |

| TLV320AIC33 | 制造商:BB 制造商全称:BB 功能描述:LOW POWER STEREO AUDIO CODEC FOR PORTABLE AUDIO/TELEPHONY |

| TLV320AIC33EVM | 功能描述:音频 IC 开发工具 Dghtr card only RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V |

发布紧急采购,3分钟左右您将得到回复。