- 您现在的位置:买卖IC网 > PDF目录98254 > TLV320AIC33IZQER (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PBGA80 PDF资料下载

参数资料

| 型号: | TLV320AIC33IZQER |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| 封装: | 5 X 5 MM, ROHS COMPLIANT, PLASTIC, VFBGA-80 |

| 文件页数: | 50/93页 |

| 文件大小: | 1427K |

| 代理商: | TLV320AIC33IZQER |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页当前第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

SLAS480B – JANUARY 2006 – REVISED DECEMBER 2008 ........................................................................................................................................... www.ti.com

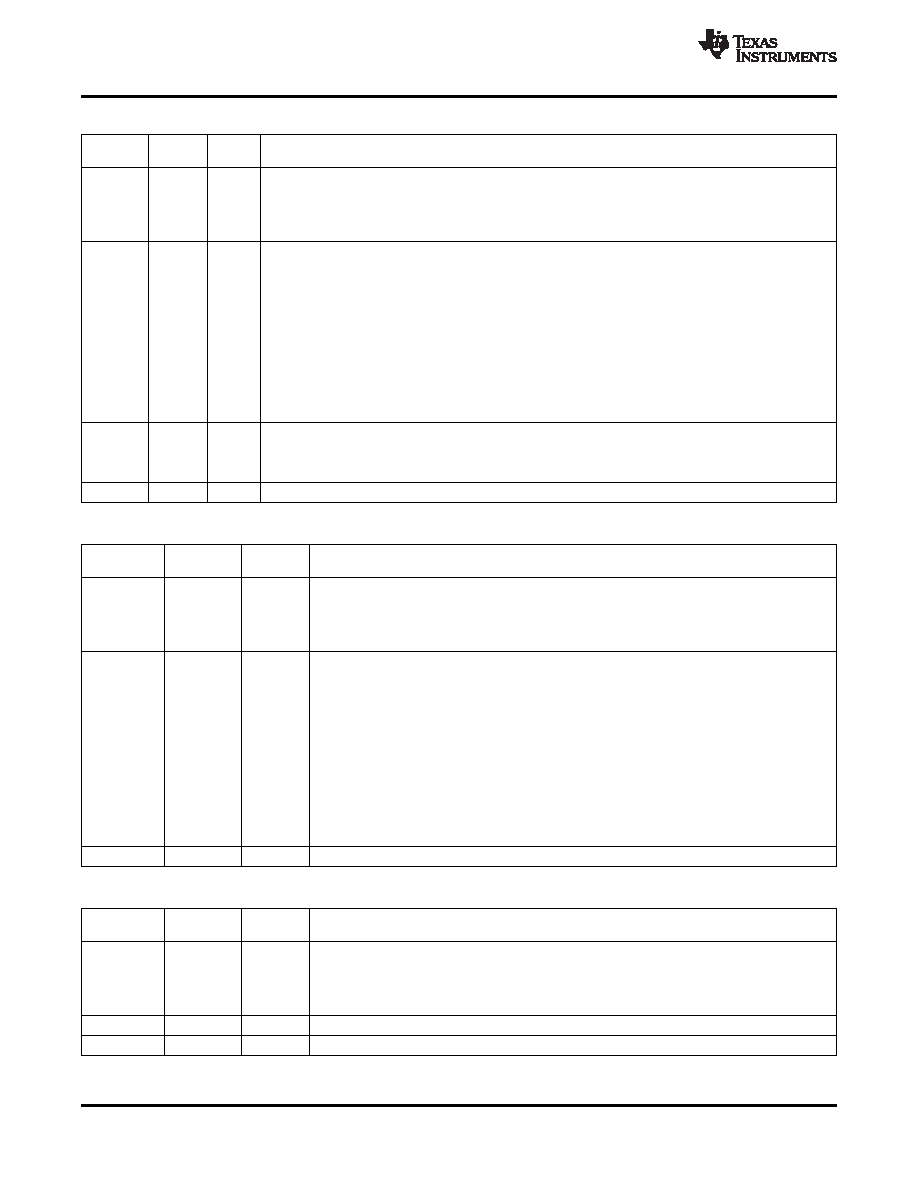

Page 0 / Register 23:

LINE2R to Right ADC Control Register

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7

R/W

0

LINE2R Single-Ended vs Fully Differential Control

If LINE2R is selected to both left and right ADC channels, both connections must use the same

configuration (single-ended or fully differential mode).

0: LINE2R is configured in single-ended mode

1: LINE2R is configured in fully differential mode

D6–D3

R/W

1111

LINE2R Input Level Control for Right ADC PGA Mix

Setting the input level control to a gain below automatically connects LINE2R to the right ADC PGA mix

0000: Input level control gain = 0.0-dB

0001: Input level control gain = -–1.5-dB

0010: Input level control gain = –3.0-dB

0011: Input level control gain = –4.5-dB

0100: Input level control gain = –6.0-dB

0101: Input level control gain = –7.5-dB

0110: Input level control gain = –9.0-dB

0111: Input level control gain = –10.5-dB

1000: Input level control gain = –12.0-dB

1001-1110: Reserved. Do not write these sequences to these register bits

1111: LINE2R is not connected to the right ADC PGA

D2

R/W

0

Right ADC Channel Weak Common-Mode Bias Control

0:

Right ADC channel unselected inputs are not biased weakly to the ADC common-mode voltage

1:

Right ADC channel unselected inputs are biased weakly to the ADC common- mode voltage

D1–D0

R

00

Reserved. Write only zeros to these register bits

Page 0 / Register 24:

LINE1L to Right ADC Control Register

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7

R/W

0

LINE1L Single-Ended vs Fully Differential Control

If LINE1L is selected to both left and right ADC channels, both connections must use the same

configuration (single-ended or fully differential mode).

0: LINE1L is configured in single-ended mode

1: LINE1L is configured in fully differential mode

D6–D3

R/W

1111

LINE1L Input Level Control for Right ADC PGA Mix

Setting the input level control to a gain below automatically connects LINE1L to the right ADC

PGA mix

0000: Input level control gain = 0.0-dB

0001: Input level control gain = –1.5-dB

0010: Input level control gain = –3.0-dB

0011: Input level control gain = –4.5-dB

0100: Input level control gain = –6.0-dB

0101: Input level control gain = –7.5-dB

0110: Input level control gain = –9.0-dB

0111: Input level control gain = –10.5-dB

1000: Input level control gain = –12.0-dB

1001–1110: Reserved. Do not write these sequences to these register bits

1111: LINE1L is not connected to the right ADC PGA

D2–D0

R

000

Reserved. Write only zeros to these register bits.

Page 0 / Register 25:

MICBIAS Control Register

BIT

READ/

RESET

DESCRIPTION

WRITE

VALUE

D7–D6

R/W

00

MICBIAS Level Control

00: MICBIAS output is powered down

01: MICBIAS output is powered to 2.0 V

10: MICBIAS output is powered to 2.5 V

11: MICBIAS output is connected to AVDD

D5–D3

R

000

Reserved. Write only zeros to these register bits.

D2–D0

R

XXX

Reserved. Write only zeros to these register bits.

54

Copyright 2006–2008, Texas Instruments Incorporated

Product Folder Link(s): TLV320AIC33

相关PDF资料 |

PDF描述 |

|---|---|

| TLV320AIC33IZQE | SPECIALTY CONSUMER CIRCUIT, PBGA80 |

| TLV320AIC33IRGZT | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| TLV320AIC33IRGZRG4 | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| TLV320AIC33IRGZTG4 | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

| TLV320AIC33IRGZ | SPECIALTY CONSUMER CIRCUIT, PQCC48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TLV320AIC33NIZQE | 制造商:Texas Instruments 功能描述: |

| TLV320AIC33NIZQER | 制造商:Texas Instruments 功能描述: |

| TLV320AIC33RHBRG4 | 制造商:Texas Instruments 功能描述:CODEC - Tape and Reel |

| TLV320AIC34 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FOUR-CHANNEL, LOW-POWER AUDIO CODEC FOR PORTABLE AUDIO/TELEPHONY |

| TLV320AIC34_1 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FOUR-CHANNEL, LOW-POWER AUDIO CODEC FOR PORTABLE AUDIO/TELEPHONY |

发布紧急采购,3分钟左右您将得到回复。