- 您现在的位置:买卖IC网 > PDF目录97770 > TPS3613-01DGST (TEXAS INSTRUMENTS INC) 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO10 PDF资料下载

参数资料

| 型号: | TPS3613-01DGST |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 电源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO10 |

| 封装: | PLASTIC, MSOP-10 |

| 文件页数: | 9/10页 |

| 文件大小: | 142K |

| 代理商: | TPS3613-01DGST |

TPS3613-01

ADJUSTABLE BATTERY-BACKUP SUPERVISOR

FOR RAM RETENTION

SLVS340 – DECEMBER 2000

8

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

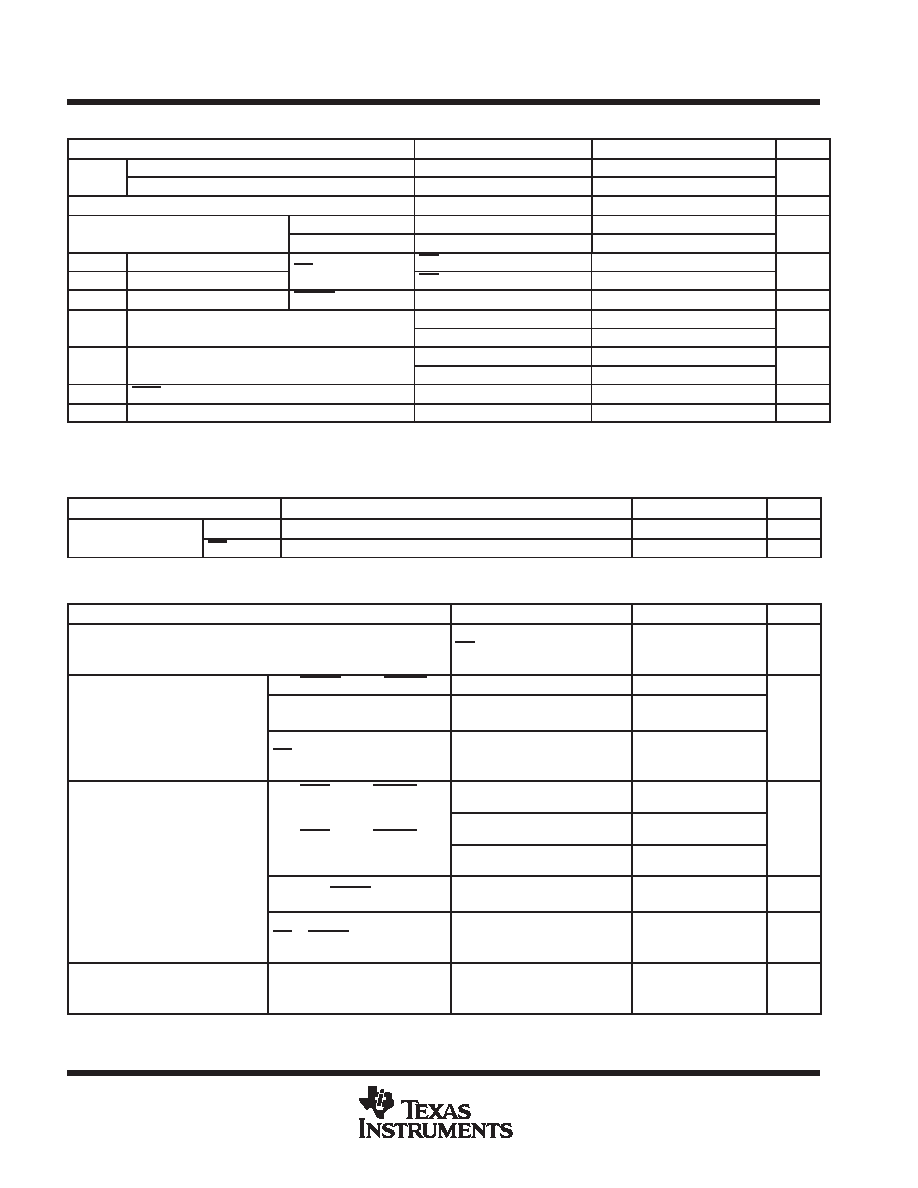

electrical characteristics over recommended operating conditions (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

RDS( )

VDD to VOUT on-resistance

VDD = 5 V

0.6

1

RDS(on)

VBAT to VOUT on-resistance

VBAT = 3.3 V

8

15

VIT

Negative-going input threshold voltage (see Note 3)

1.13

1.15

1.17

V

Vh

Hysteresis

Sense

1.1 V

< VIT < 1.65 V

12

mV

Vhys

Hysteresis

VBSW (see Note 4)

VDD = 1.8 V

55

mV

IIH

High-level input current

MR

MR = 0.7 x VDD, VDD = 5.0 V

–33

–76

A

IIL

Low-level input current

MR

MR = 0 V, VDD = 5.0 V

–110

–255

A

II

Input current

SENSE

VDD = 1.15 V

–25

25

nA

IDD

VDD supply current

VOUT = VDD

40

A

IDD

VDD supply current

VOUT = VBAT

40

A

IBAT

VBAT supply current

VOUT = VDD

–0.1

0.1

A

IBAT

VBAT supply current

VOUT = VBAT

0.5

A

Ilkg

CEIN leakage current

Disable mode, VI < VDD

±1

A

Ci

Input capacitance

VI = 0 V to 5 V

5

pF

NOTES:

3. To ensure best stability of the threshold voltage, a bypass capacitor (ceramic, 0.1

F) should be placed near to the supply terminals.

4. For VDD < 1.6 V, VOUT switches to VBAT regardless of VBAT

timing requirements at RL = 1 M, CL = 50 pF, TA = –40°C to 85°C

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

t

Pulse width

SENSE

VIH = VIT + 0.2 V,

VIL = VIT – 0.2 V

6

s

tw

Pulse width

MR

VSENSE > VIT + 0.2 V VIL = 0.3 x VDD, VIH = 0.7 x VDD

100

ns

switching characteristics at RL = 1 M, CL= 50 pF, TA = –40°C to 85°C

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

td

Delay time

VSENSE ≥ VIT + 0.2 V,

MR

≥ 0.7 x VDD,

See timing diagram

60

100

140

ms

50% RESET to 50% CEOUT

VOUT = VIT

15

tPLH

Propagation (delay) time,

SENSE to RESET

VIL = VIT – 0.2 V,

VIH = VIT + 0.2 V

2

5

s

tPLH

g

(

y)

,

low-to-high-level output

MR to RESET

VSENSE ≥ VIT + 0.2 V,

VIL = 0.3 x VDD,

VIH = 0.7 x VDD

0.1

1

s

50% CEIN to 50% CEOUT,

CL = 50 pF only (see Figure 3)

VDD = 1.8 V

5

15

CL = 50 F only (see Figure 3)

(see Note 5)

50% CEIN to 50% CEOUT,

VDD = 3.3 V

1.6

5

ns

tPHL

Propagation (delay) time,

hi h t l

l

t

50% CEIN to 50% CEOUT,

CL = 50 pF only (see Figure 3)

(see Note 5)

VDD = 5 V

1

3

tPHL

g(

y)

high-to-low-level output

SENSE to RESET

VIL = VIT – 0.2 V,

VIH = VIT + 0.2 V

2

5

s

MR to RESET

VSENSE ≥ VIT + 0.2 V,

VIL = 0.3 x VDD,

VIH = 0.7 x VDD

0.1

1

s

Transition time

VDD to VBAT

VIH =VBAT + 0.2 V,

VIL = VBAT – 0.2 V,

VBAT < VIT

3

s

NOTE 5: Assured by design

相关PDF资料 |

PDF描述 |

|---|---|

| TPS658610ZQZT | 11-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA120 |

| TPS658610ZQZR | 11-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA120 |

| TPSCC6.5MB-TC10 | 2 SECTIONS - 2 SECTIONS, 6.5 MHz, CERAMIC BRF |

| TPSCC6.0MB-TC10 | 2 SECTIONS - 2 SECTIONS, 6 MHz, CERAMIC BRF |

| TPSCC5.5MB-TC10 | 2 SECTIONS - 2 SECTIONS, 5.5 MHz, CERAMIC BRF |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TPS3613-18DGSR | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| TPS3613-18DGST | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| TPS3613-25DGSR | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| TPS3613-25DGST | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| TPS3613-30DGSR | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

发布紧急采购,3分钟左右您将得到回复。