- 您现在的位置:买卖IC网 > PDF目录69523 > TPS84410RKGT (TEXAS INSTRUMENTS INC) 4 A SWITCHING REGULATOR, 600 kHz SWITCHING FREQ-MAX, PQCC39 PDF资料下载

参数资料

| 型号: | TPS84410RKGT |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 稳压器 |

| 英文描述: | 4 A SWITCHING REGULATOR, 600 kHz SWITCHING FREQ-MAX, PQCC39 |

| 封装: | 9 X 11 MM, 2.80 MM HEIGHT, GREEN, PLASTIC, BQFN-39 |

| 文件页数: | 21/26页 |

| 文件大小: | 819K |

| 代理商: | TPS84410RKGT |

SLVSAR5

– SEPTEMBER 2011

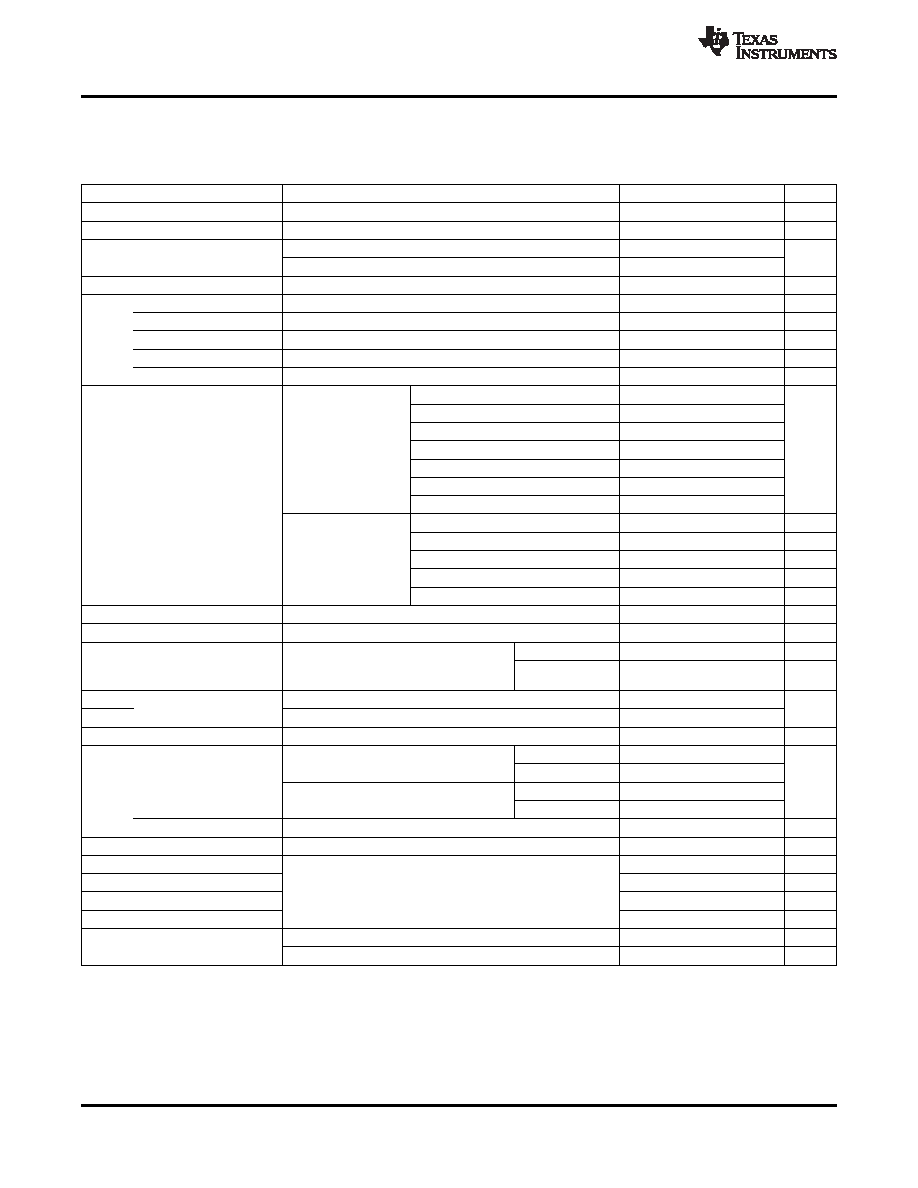

ELECTRICAL CHARACTERISTICS

Over -40

°C to 85°C free-air temperature, VIN = 3.3 V, VOUT = 1.8 V, IOUT = 4A,

CIN1 = 47 F ceramic, CIN2 = 220 F poly-tantalum, COUT1 = 47 F ceramic, COUT2 = 100 F poly-tantalum (unless otherwise

noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

IOUT

Output current

TA = 85°C, natural convection

0

4

A

VIN

Input voltage range

Over IOUT range

2.95(1)

6

V

VIN = increasing

3.05

3.135

UVLO

VIN Undervoltage lockout

V

VIN = decreasing

2.5

2.75

VOUT(adj)

Output voltage adjust range

Over IOUT range

0.8

3.6

V

Set-point voltage tolerance

TA = 25°C, IOUT = 0A

±1.0% (2)

Temperature variation

-40

°C ≤ TA ≤ +85°C, IOUT = 0A

±0.3%

VOUT

Line regulation

Over VIN range, TA = 25°C, IOUT = 0A

±0.1%

Load regulation

Over IOUT range, TA = 25°C

±0.1%

Total output voltage variation

Includes set-point, line, load, and temperature variation

±1.5% (2)

VOUT = 3.3V, fSW = 1 MHz

95%

VOUT = 2.5V, fSW = 1 MHz

93%

VOUT = 1.8V, fSW = 1 MHz

91%

VIN = 5 V

VOUT = 1.5V, fSW = 1 MHz

89%

IO = 2 A

VOUT = 1.2V, fSW =750 kHz

87%

VOUT = 1.0V, fSW = 650 kHz

85%

η

Efficiency

VOUT = 0.8V, fSW = 650 kHz

84%

VIN = 3.3V

VOUT = 1.8V, fSW = 1 MHz

90%

IO = 2 A

VOUT = 1.5V, fSW = 1 MHz

88%

VOUT = 1.2V, fSW = 750 kHz

87%

VOUT = 1.0V, fSW = 650 kHz

84%

VOUT = 0.8V, fSW = 650 kHz

82%

Output voltage ripple

20 MHz bandwith

9

mVPP

ILIM

Overcurrent threshold

7

A

Recovery time

80

s

Transient response

1.0 A/

s load step from 1A to 3A

VOUT

90

mV

over/undershoot

VINH-H

Inhibit High Voltage

1.25

Open (3)

Inhibit Control

V

VINH-L

Inhibit Low Voltage

–0.3

1.0

II(stby)

Input standby current

INH pin to AGND

70

100

A

Good

93%

VOUT rising

Fault

107%

PWRGD Thresholds

Power

Fault

91%

Good

VOUT falling

Good

105%

PWRGD Low Voltage

I(PWRGD) = 0.33 mA

0.3

V

fSW

Switching frequency

Over VIN and IOUT ranges, RT/CLK pin OPEN

400

500

600

kHz

fCLK

Synchronization frequency

500

2000

kHz

VCLK-H

CLK High-Level Threshold

2.2

3.3

V

CLK Control

VCLK-L

CLK Low-Level Threshold

-0.3

0.4

V

CLK_PW CLK Pulse Width

75(4)

ns

Thermal shutdown

175

°C

Thermal Shutdown

Thermal shutdown hysteresis

15

°C

(1)

The minimum VIN voltage is 2.95V or (VOUT + 1.1V) , whichever is greater. A 5V input bus is recommended for output voltages greater

than 2V.

(2)

The stated limit of the set-point voltage tolerance includes the tolerance of both the internal voltage reference and the internal

adjustment resistor. The overall output voltage tolerance will be affected by the tolerance of the external RSET resistor.

(3)

This control pin has an internal pullup. Do not place an external pull-up resistor on this pin. If this pin is left open circuit, the device

operates when input power is applied. A small low-leakage MOSFET is recommended for control. See the application section for further

guidance.

(4)

The maximum synchronization clock pulse width is dependant on VIN, VOUT, and the synchronization frequency. See the

Synchronization (CLK) section for more information.

4

Copyright

2011, Texas Instruments Incorporated

相关PDF资料 |

PDF描述 |

|---|---|

| TPS84410RKGR | 4 A SWITCHING REGULATOR, 600 kHz SWITCHING FREQ-MAX, PQCC39 |

| TQN25A48S12 | 1-OUTPUT 300 W DC-DC REG PWR SUPPLY MODULE |

| TQN25A48S12 | 1-OUTPUT 300 W DC-DC REG PWR SUPPLY MODULE |

| TQN20A48S12 | 1-OUTPUT 240 W DC-DC REG PWR SUPPLY MODULE |

| TRF2020PW | PLL FREQUENCY SYNTHESIZER, 1200 MHz, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TPS844F | 制造商:TOSHIBA 制造商全称:Toshiba Semiconductor 功能描述:Silicon Epitaxial Planar |

| TPS84610 | 制造商:TI 制造商全称:Texas Instruments 功能描述:2.95-V to 6-V Input, 6-A Synchronous Buck, Integrated Power Solution |

| TPS84610EVM-003 | 功能描述:电源管理IC开发工具 TPS84610 Eval Mod RoHS:否 制造商:Maxim Integrated 产品:Evaluation Kits 类型:Battery Management 工具用于评估:MAX17710GB 输入电压: 输出电压:1.8 V |

| TPS84610RKG | 制造商:TI 制造商全称:Texas Instruments 功能描述:2-A to 6-A Integrated Power Solution |

| TPS84610RKGR | 功能描述:直流/直流开关转换器 3-6Vin,6A Sync Buck Integr Pwr Sol RoHS:否 制造商:STMicroelectronics 最大输入电压:4.5 V 开关频率:1.5 MHz 输出电压:4.6 V 输出电流:250 mA 输出端数量:2 最大工作温度:+ 85 C 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。