- 您现在的位置:买卖IC网 > PDF目录69524 > TRF3761-BIRHAR (TEXAS INSTRUMENTS INC) PLL FREQUENCY SYNTHESIZER, 104 MHz, PQCC40 PDF资料下载

参数资料

| 型号: | TRF3761-BIRHAR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 104 MHz, PQCC40 |

| 封装: | GREEN, PLASTIC, MO-220VJJD-2, QFN-40 |

| 文件页数: | 30/60页 |

| 文件大小: | 1736K |

| 代理商: | TRF3761-BIRHAR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

SLWS181J – OCTOBER 2005 – REVISED AUGUST 2008 ............................................................................................................................................... www.ti.com

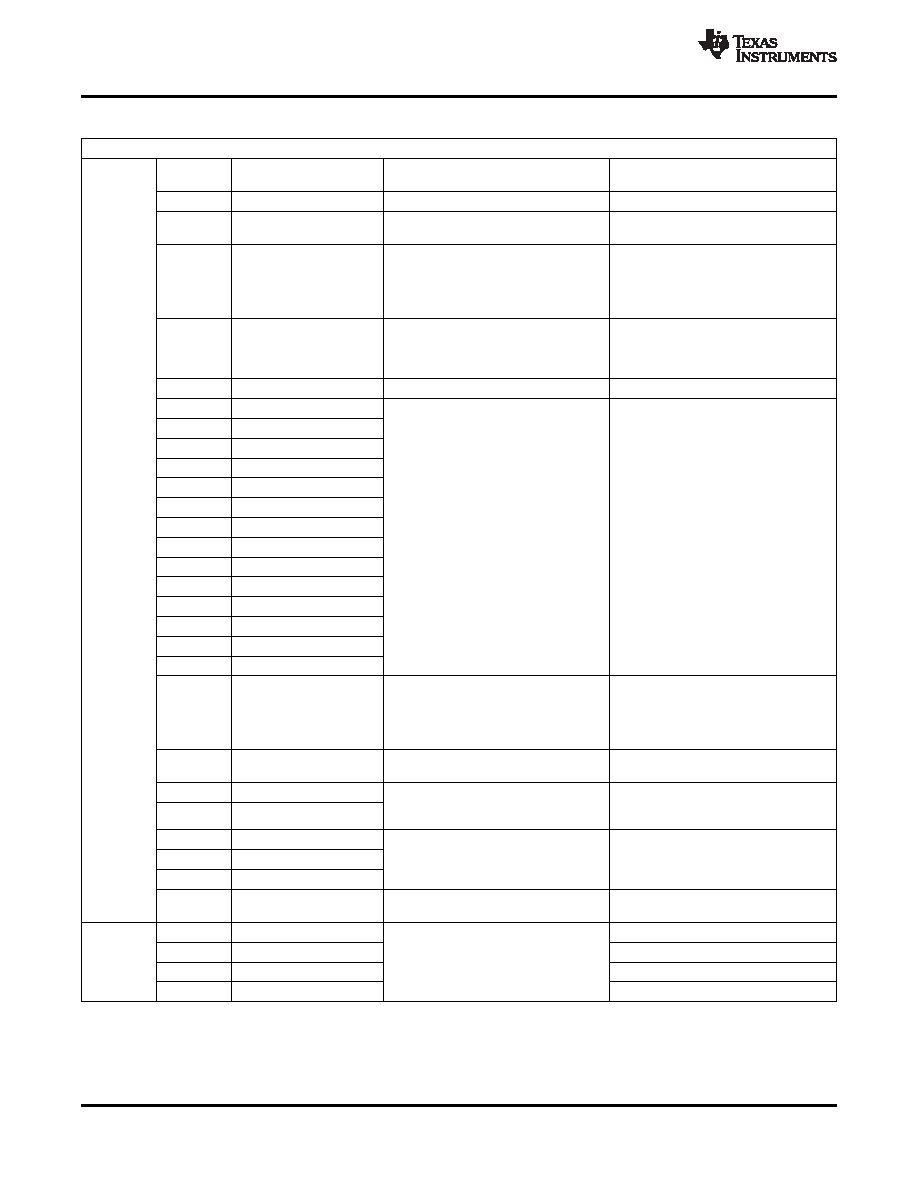

Table 1. Register 1: Device Setup

REGISTER 1 MAPPING

Data Field

DB31

FULL_CAL_REQ

This is a read only bit, that indicates if a

0 power-up cal is not required

power-up cal is required

1 power-up cal is required

DB30

CP_TEST

TI internal use only

1 test enabled

DB29

TRIS_CP

High-impedance state charge pump

1 CP high-impedance state

output

0 for normal operation

DB28

PFD_POL

Selects Polarity of PFD, should match

0 negative

polarity of VCO gain. If using external

1 positive

VCO with Negative gain then set to 0

and vise versa. The internal VCO has

positive gain so set to positve(1)

DB27

ABPW1

ABPW<1,0>: anti-backlash pulse width

00 1.5ns delay

01 0.9ns delay

10 3.8ns delay

11 2.7ns delay

DB26

ABPW0

DB25

RDIV_13

14-bit reference clock divider

RDIV<13,0>:00...01: divide by 1

RDIV<13,0>:00...10: divide by 2

DB24

RDIV_12

RDIV<13,0>:00...11: divide by 3

DB23

RDIV_11

DB22

RDIV_10

DB21

RDIV_9

DB20

RDIV_8

DB19

RDIV_7

DB18

RDIV_6

DB17

RDIV_5

DB16

RDIV_4

DB15

RDIV_3

DB14

RDIV_2

DB13

RDIV_1

DB12

RDIV_0

DB11

PD_BUFOUT

If DB10 = 0 then it controls power down

<DB10:11>:

of output buffer

00 default; output buffer on

01 output buffer off

1x output buffer on/off controlled by

OUTBUF_EN pin

DB10

OUTBUF_EN_SEL

Select Output Buffer enable control:

0 internal

1 through OUTBUF_EN pin

DB9

OUT_MODE_1

OUTBUFMODE<1,0>: Selection of RF

00 divide by 1

output buffer division ratio

01 divide by 2

DB8

OUT_MODE_0

10 divide by4

DB7

ICP2

ICP<2,0>: select charge pump current

(1 mA step). From 1.4mA to 11.2mA

DB6

ICP1

with Rbias set to 2.37Kohms.

DB5

ICP0

DB4

RESET

Registers reset

1 high

0 low for normal operation

Address

DB3

Address Bits <3,0>=0000 for register 1

Bits

DB2

DB1

DB0

36

Copyright 2005–2008, Texas Instruments Incorporated

Product Folder Link(s): TRF3761

相关PDF资料 |

PDF描述 |

|---|---|

| TRF3761-KIRHAT | PLL FREQUENCY SYNTHESIZER, 104 MHz, PQCC40 |

| TRF3761-KIRHAR | PLL FREQUENCY SYNTHESIZER, 104 MHz, PQCC40 |

| TRF3761IRHAR | PLL FREQUENCY SYNTHESIZER, 104 MHz, PQCC40 |

| TRU050-GACCA16.384-8.192 | PHASE LOCKED LOOP, CDSO16 |

| TRU050-GACFA33.330-16.665 | PHASE LOCKED LOOP, CDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TRF3761-BIRHARG4 | 功能描述:时钟合成器/抖动清除器 Low Noise Integer N PLL Freq Synth RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| TRF3761-BIRHAT | 功能描述:时钟合成器/抖动清除器 Low Noise Integer N PLL Freq Synth RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| TRF3761-BIRHATG4 | 功能描述:时钟合成器/抖动清除器 Low Noise Integer N PLL Freq Synth RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| TRF3761-C | 制造商:TI 制造商全称:Texas Instruments 功能描述:INTEGER-N PLL WITH INTEGRATED VCO |

| TRF3761-CIRHAR | 功能描述:时钟合成器/抖动清除器 Low Noise Integer N PLL Freq Synth RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。