参数资料

| 型号: | TS80C51RD2-MCA |

| 厂商: | Atmel |

| 文件页数: | 22/84页 |

| 文件大小: | 0K |

| 描述: | IC MCU 8BIT 768BYTE 40MHZ 40-DIP |

| 标准包装: | 216 |

| 系列: | 80C |

| 核心处理器: | 8051 |

| 芯体尺寸: | 8-位 |

| 速度: | 40/20MHz |

| 连通性: | UART/USART |

| 外围设备: | POR,PWM,WDT |

| 输入/输出数: | 32 |

| 程序存储器类型: | ROMless |

| RAM 容量: | 768 x 8 |

| 电压 - 电源 (Vcc/Vdd): | 4.5 V ~ 5.5 V |

| 振荡器型: | 内部 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 40-DIP(0.600",15.24mm) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

DS70292G-page 30

2007-2012 Microchip Technology Inc.

3.7

Arithmetic Logic Unit (ALU)

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/

X04, and dsPIC33FJ128GPX02/X04 ALU is 16 bits

wide and is capable of addition, subtraction, bit shifts

and logic operations. Unless otherwise mentioned,

arithmetic operations are two’s complement in nature.

Depending on the operation, the ALU can affect the

values of the Carry (C), Zero (Z), Negative (N),

Overflow (OV) and Digit Carry (DC) Status bits in the

SR register. The C and DC Status bits operate as

Borrow and Digit Borrow bits, respectively, for

subtraction operations.

The ALU can perform 8-bit or 16-bit operations,

depending on the mode of the instruction that is used.

Data for the ALU operation can come from the W

register array or data memory, depending on the

addressing mode of the instruction. Likewise, output

data from the ALU can be written to the W register array

or a data memory location.

Refer to the “16-bit MCU and DSC Programmer’s Ref-

erence Manual” (DS70157) for information on the SR

bits affected by each instruction.

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/

X04, and dsPIC33FJ128GPX02/X04 CPU incorpo-

rates hardware support for both multiplication and divi-

sion. This includes a dedicated hardware multiplier and

support hardware for 16-bit-divisor division.

3.7.1

MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the

DSP engine, the ALU supports unsigned, signed or

mixed-sign operation in several MCU multiplication

modes:

16-bit x 16-bit signed

16-bit x 16-bit unsigned

16-bit signed x 5-bit (literal) unsigned

16-bit unsigned x 16-bit unsigned

16-bit unsigned x 5-bit (literal) unsigned

16-bit unsigned x 16-bit signed

8-bit unsigned x 8-bit unsigned

3.7.2

DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit

signed and unsigned integer divide operations with the

following data sizes:

1.

32-bit signed/16-bit signed divide

2.

32-bit unsigned/16-bit unsigned divide

3.

16-bit signed/16-bit signed divide

4.

16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0

and the remainder in W1. 16-bit signed and unsigned

DIV instructions can specify any W register for both

the 16-bit divisor (Wn) and any W register (aligned)

pair (W(m + 1):Wm) for the 32-bit dividend. The divide

algorithm takes one cycle per bit of divisor, so both

32-bit/16-bit and 16-bit/16-bit instructions take the

same number of cycles to execute.

3.8

DSP Engine

The DSP engine consists of a high-speed 17-bit x

17-bit multiplier, a barrel shifter and a 40-bit adder/

subtracter (with two target accumulators, round and

saturation logic).

The dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/

X04, and dsPIC33FJ128GPX02/X04 is a single-cycle

instruction flow architecture; therefore, concurrent

operation of the DSP engine with MCU instruction flow

is not possible. However, some MCU ALU and DSP

engine resources can be used concurrently by the

same instruction (e.g., ED, EDAC).

The DSP engine can also perform inherent accumula-

tor-to-accumulator operations that require no additional

data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in

the CPU Core Control register (CORCON), as listed

below:

Fractional or integer DSP multiply (IF)

Signed or unsigned DSP multiply (US)

Conventional or convergent rounding (RND)

Automatic saturation on/off for ACCA (SATA)

Automatic saturation on/off for ACCB (SATB)

Automatic saturation on/off for writes to data

memory (SATDW)

Accumulator Saturation mode selection (ACC-

SAT)

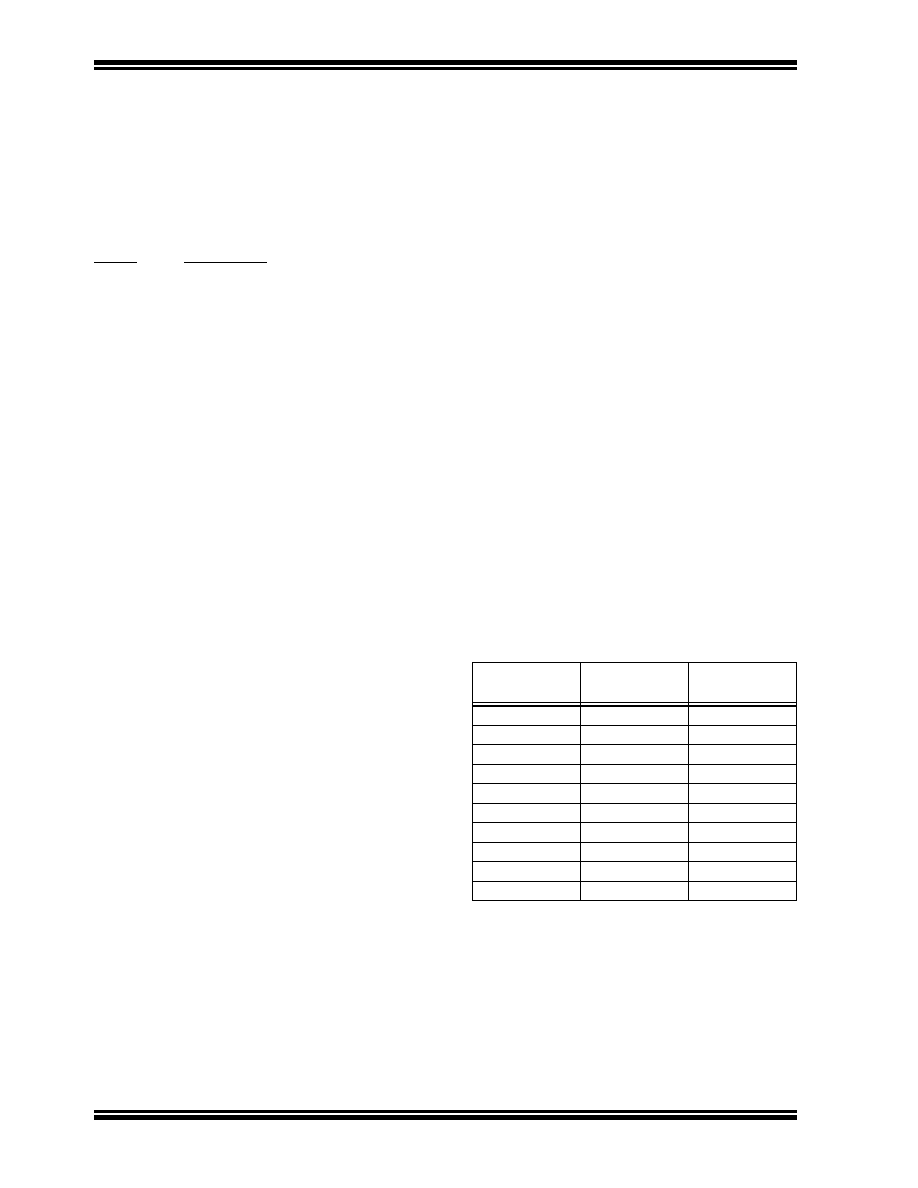

A block diagram of the DSP engine is shown in

TABLE 3-1:

DSP INSTRUCTIONS

SUMMARY

Instruction

Algebraic

Operation

ACC Write

Back

CLR

A = 0

Yes

ED

A = (x – y)2

No

EDAC

A = A + (x – y)2

No

MAC

A = A + (x y)

Yes

MAC

A = A + x2

No

MOVSAC

No change in A

Yes

MPY

A = x y

No

MPY

A = x 2

No

MPY.N

A = – x y

No

MSC

A = A – x y

Yes

相关PDF资料 |

PDF描述 |

|---|---|

| TS87C54X2-LIA | IC MCU 8BIT 16K OTP 30MHZ 40-DIP |

| 52559-1670 | CONN FFC 16POS .5MM VERT ZIF SMD |

| TS80C31X2-VIA | IC MCU 8BIT 40/30MHZ 40-DIP |

| TS87C51RB2-LIA | IC MCU 8BIT 16K OTP 30MHZ 40-DIP |

| TS80C51RD2-LCA | IC MCU 8BIT 768BYTE 30MHZ 40-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TS80C51RD2-MCAD | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| TS80C51RD2-MCB | 功能描述:IC MCU 8BIT 768BYTE 40MHZ 44PLCC RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:80C 标准包装:1,500 系列:AVR® ATtiny 核心处理器:AVR 芯体尺寸:8-位 速度:16MHz 连通性:I²C,LIN,SPI,UART/USART,USI 外围设备:欠压检测/复位,POR,PWM,温度传感器,WDT 输入/输出数:16 程序存储器容量:8KB(4K x 16) 程序存储器类型:闪存 EEPROM 大小:512 x 8 RAM 容量:512 x 8 电压 - 电源 (Vcc/Vdd):2.7 V ~ 5.5 V 数据转换器:A/D 11x10b 振荡器型:内部 工作温度:-40°C ~ 125°C 封装/外壳:20-SOIC(0.295",7.50mm 宽) 包装:带卷 (TR) |

| TS80C51RD2-MCBB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| TS80C51RD2-MCBD | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| TS80C51RD2-MCBR | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。