参数资料

| 型号: | TS80C51RD2-MCA |

| 厂商: | Atmel |

| 文件页数: | 56/84页 |

| 文件大小: | 0K |

| 描述: | IC MCU 8BIT 768BYTE 40MHZ 40-DIP |

| 标准包装: | 216 |

| 系列: | 80C |

| 核心处理器: | 8051 |

| 芯体尺寸: | 8-位 |

| 速度: | 40/20MHz |

| 连通性: | UART/USART |

| 外围设备: | POR,PWM,WDT |

| 输入/输出数: | 32 |

| 程序存储器类型: | ROMless |

| RAM 容量: | 768 x 8 |

| 电压 - 电源 (Vcc/Vdd): | 4.5 V ~ 5.5 V |

| 振荡器型: | 内部 |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 40-DIP(0.600",15.24mm) |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

2007-2012 Microchip Technology Inc.

DS70292G-page 61

dsPIC33FJ32GP302/304, dsPIC33FJ64GPX02/X04, AND dsPIC33FJ128GPX02/X04

4.4.1

SOFTWARE STACK

In addition to its use as a working register, the W15

register

in

the

dsPIC33FJ32GP302/304,

dsPIC33FJ64GPX02/X04, and dsPIC33FJ128GPX02/

X04 devices is also used as a software Stack Pointer.

The Stack Pointer always points to the first available

free word and grows from lower to higher addresses. It

pre-decrements for stack pops and post-increments for

stack pushes, as shown in Figure 4-6. For a PC push

during any CALL instruction, the MSb of the PC is zero-

extended before the push, ensuring that the MSb is

always clear.

The Stack Pointer Limit register (SPLIM) associated

with the Stack Pointer sets an upper address boundary

for the stack. SPLIM is uninitialized at Reset. As is the

case for the Stack Pointer, SPLIM<0> is forced to ‘0’

because all stack operations must be word aligned.

Whenever an EA is generated using W15 as a source

or destination pointer, the resulting address is

compared with the value in SPLIM. If the contents of

the Stack Pointer (W15) and the SPLIM register are

equal and a push operation is performed, a stack error

trap does not occur. The stack error trap occurs on a

subsequent push operation. For example, to cause a

stack error trap when the stack grows beyond address

0x2000 in RAM, initialize the SPLIM with the value

0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is

generated when the Stack Pointer address is found to

be less than 0x0800. This prevents the stack from

interfering with the Special Function Register (SFR)

space.

A write to the SPLIM register should not be immediately

followed by an indirect read operation using W15.

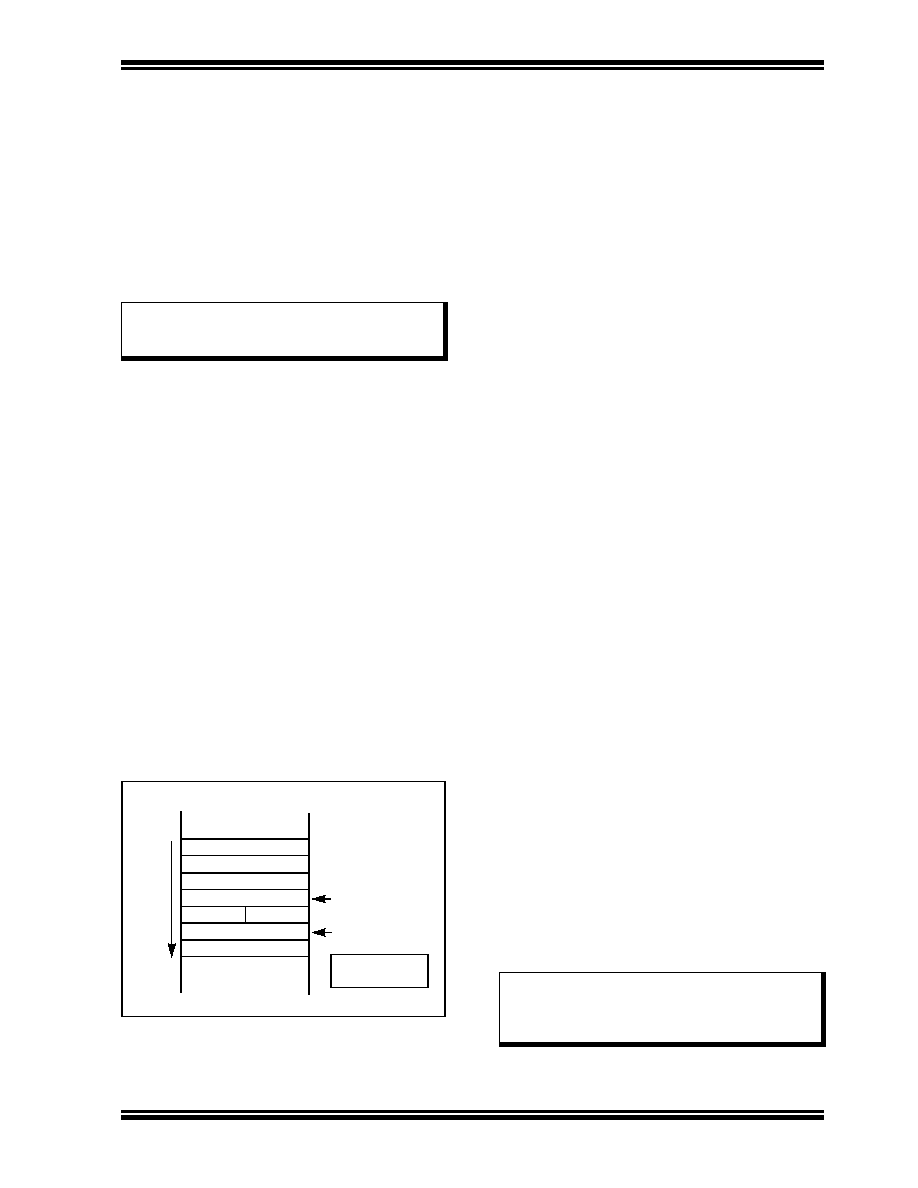

FIGURE 4-6:

CALL STACK FRAME

4.4.2

DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM

protection features that enable segments of RAM to be

protected when used in conjunction with Boot and

Secure Code Segment Security. BSRAM (Secure RAM

segment for BS) is accessible only from the Boot

Segment Flash code when enabled. SSRAM (Secure

RAM segment for RAM) is accessible only from the

Secure Segment Flash code when enabled. See

Table 4-1 for an overview of the BSRAM and SSRAM

SFRs.

4.5

Instruction Addressing Modes

The addressing modes shown in Table 4-37 form the

basis of the addressing modes optimized to support the

specific features of individual instructions. The

addressing modes provided in the MAC class of

instructions differ from those in the other instruction

types.

4.5.1

FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field

(f) to directly address data present in the first 8192

bytes of data memory (near data space). Most file

register instructions employ a working register, W0,

which is denoted as WREG in these instructions. The

destination is typically either the same file register or

WREG (with the exception of the MUL instruction),

which writes the result to a register or register pair. The

MOV instruction allows additional flexibility and can

access the entire data space.

4.5.2

MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where:

Operand 1 is always a working register (that is, the

addressing mode can only be register direct), which is

referred to as Wb.

Operand 2 can be a W register, fetched from data

memory, or a 5-bit literal. The result location can be

either a W register or a data memory location. The fol-

lowing addressing modes are supported by MCU

instructions:

Register Direct

Register Indirect

Register Indirect Post-Modified

Register Indirect Pre-Modified

5-bit or 10-bit Literal

Note:

A PC push during exception processing

concatenates the SRL register to the MSb

of the PC prior to the push.

<Free Word>

PC<15:0>

000000000

0

15

W15 (before CALL)

W15 (after CALL)

S

ta

ck

Gr

ow

sT

o

war

d

H

igh

er

A

ddr

es

s

0x0000

PC<22:16>

POP : [--W15]

PUSH : [W15++]

Note:

Not all instructions support all the

addressing modes given above. Individual

instructions can support different subsets

of these addressing modes.

相关PDF资料 |

PDF描述 |

|---|---|

| TS87C54X2-LIA | IC MCU 8BIT 16K OTP 30MHZ 40-DIP |

| 52559-1670 | CONN FFC 16POS .5MM VERT ZIF SMD |

| TS80C31X2-VIA | IC MCU 8BIT 40/30MHZ 40-DIP |

| TS87C51RB2-LIA | IC MCU 8BIT 16K OTP 30MHZ 40-DIP |

| TS80C51RD2-LCA | IC MCU 8BIT 768BYTE 30MHZ 40-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TS80C51RD2-MCAD | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| TS80C51RD2-MCB | 功能描述:IC MCU 8BIT 768BYTE 40MHZ 44PLCC RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:80C 标准包装:1,500 系列:AVR® ATtiny 核心处理器:AVR 芯体尺寸:8-位 速度:16MHz 连通性:I²C,LIN,SPI,UART/USART,USI 外围设备:欠压检测/复位,POR,PWM,温度传感器,WDT 输入/输出数:16 程序存储器容量:8KB(4K x 16) 程序存储器类型:闪存 EEPROM 大小:512 x 8 RAM 容量:512 x 8 电压 - 电源 (Vcc/Vdd):2.7 V ~ 5.5 V 数据转换器:A/D 11x10b 振荡器型:内部 工作温度:-40°C ~ 125°C 封装/外壳:20-SOIC(0.295",7.50mm 宽) 包装:带卷 (TR) |

| TS80C51RD2-MCBB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| TS80C51RD2-MCBD | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| TS80C51RD2-MCBR | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。