- 您现在的位置:买卖IC网 > PDF目录365968 > TSB14C01MHV IC APEX 20KE FPGA 160K 484-FBGA PDF资料下载

参数资料

| 型号: | TSB14C01MHV |

| 英文描述: | IC APEX 20KE FPGA 160K 484-FBGA |

| 中文描述: | 收发器 |

| 文件页数: | 21/35页 |

| 文件大小: | 224K |

| 代理商: | TSB14C01MHV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页当前第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

6

–

1

6 Principles of Operation

6.1

PHY/Link Interface Operation

The TSB14AA1A is designed to operate with link layer controllers (LLC) such as the Texas Instruments TSB12LV01B,

TSB12LV21B, and TSB12LV32. Details of operation for the Texas Instruments LLC devices are found in the

respective LLC data sheets. The following paragraphs describe the operation of the PHY-LLC interface.

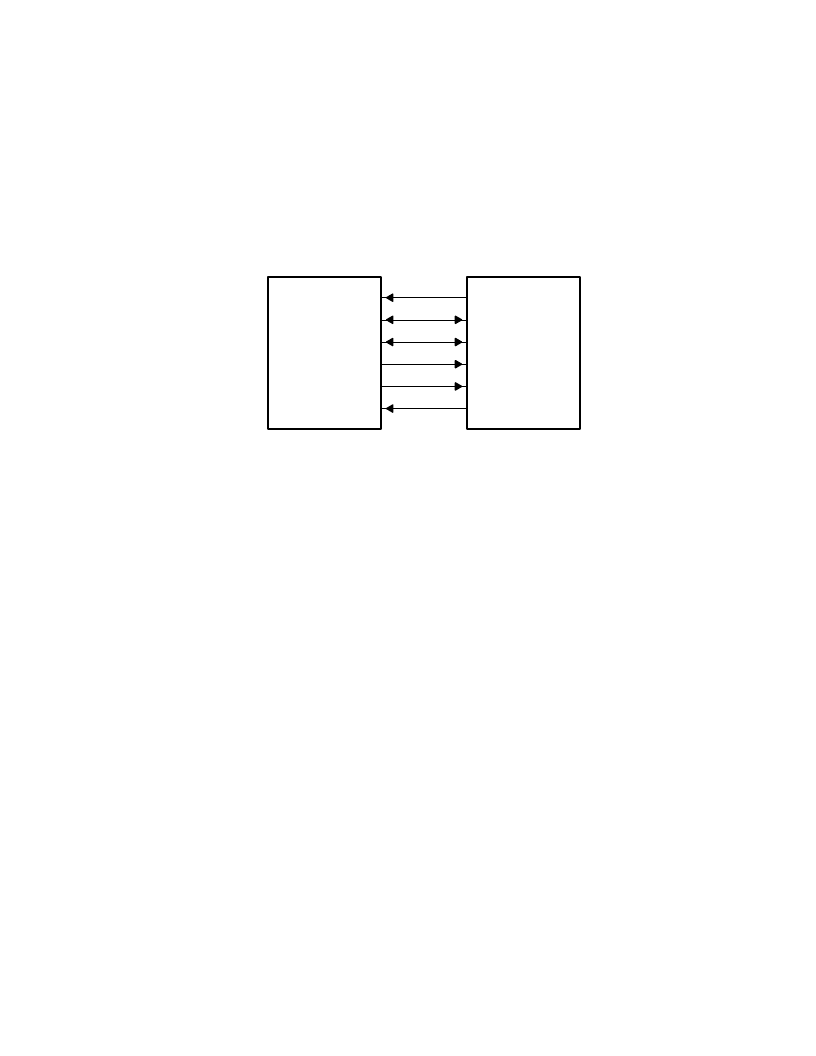

The interface to the LLC consists of the SCLK, CTL0

–

CTL1, D0

–

D1, LREQ, LPS, and LINKON terminals on the

TSB14AA1A, as shown in Figure 6

–

1.

Link Layer

Controller

SCLK

CTL0

–

CTL1

D0

–

D1

LREQ

LPS

LINKON

TSB14AA1A

Figure 6

–

1. Block Diagram of the TSB14AA1A/LLC Interface

The SCLK terminal provides either a 49.152-MHz interface clock for S100 data transfers or 24.576-MHz interface

clock for S50 data transfers. All control and data signals are synchronized to, and sampled on, the rising edge of

SCLK.

The CTL0 and CTL1 terminals form a bidirectional control bus, which controls the flow of information and data

between the TSB14AA1A and the LLC.

The D0 and D1 terminals form a bidirectional data bus, which is used to transfer status information, control

information, or packet data between the devices. The TSB14AA1A supports S50 and S100 data transfers over the

D0 and D1 data bus.

The LREQ terminal is controlled by the LLC to send serial service requests to the PHY in order to request access

to read or write internal PHY registers, or to ask the PHY to initiate a transmit action. The PHY initiates a receive action

whenever a packet is received from the serial bus.

The LPS and LINKON terminals are used for power management of the PHY and LLC. The LPS terminal indicates

the power status of the LLC, and may be used to reset the PHY-LLC interface or to disable SCLK. The LINKON

terminal is used to send a wake-up notification to the LLC and to indicate an interrupt to the LLC when LPS is inactive.

Note that not all LLCs contain a LINKON terminal, though an external circuit to operate the wake-up mode may always

be implemented at the discretion of the designer.

The TSB14AA1A normally controls the CTL0

–

CTL1 and D0

–

D1 bidirectional busses. The LLC is allowed to drive

these buses only after the LCC has been granted permission to do so by the PHY.

There are four operations that may occur on the PHY-LLC interface: link service request, status transfer, data

transmit, and data receive. The LLC issues a link service request to read or write a PHY register, or to request the

PHY to gain control of the serial-bus in order to transmit a packet.

The PHY may initiate a status transfer either autonomously or in response to a register request from the LLC.

The PHY initiates a data transmit operation after winning control of the serial-bus following a bus-request by the LLC.

The data transmit operation is initiated when the PHY grants control of the interface to the LLC.

The PHY initiates a data receive operation whenever a packet is received from the serial-bus.

The encoding of the CTL0

–

CTL1 bus is shown in Table 6

–

1 and Table 6

–

2.

相关PDF资料 |

PDF描述 |

|---|---|

| TSB14C01HV | 5-V IEEE 1394-1995 BACKPLANE TRANSCEIVER/ARBITER |

| TSB21LV03MHV | IC APEX 20KE FPGA 200K 484-FBGA |

| TSB21LV03CHV | IEEE 1394-1995 TRIPLE-CABLE TRANSCEIVER/ARBITER |

| TSB2203X6MMX30M | IC APEX 20KE FPGA 200K 240-PQFP |

| TSB2204.5X12MMX20M | IC APEX 20KE FPGA 200K 240-PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSB14C01PM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TSB15 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:EURO TERMINAL BLOCKS |

| TSB150002DS | 制造商:TE Connectivity 功能描述: |

| TSB150004DS | 制造商:TE Connectivity 功能描述:Conn Europa Terminal Blocks 8 POS 13.5mm Screw ST Cable Mount 40A/Contact |

| TSB150005 | 功能描述:栅栏接线端子 5P TERM BLOCK 13.5MM 300V 40A RoHS:否 制造商:TE Connectivity / AMP 产品:Barrier Terminal Blocks 系列: 类型:Dual Barrier, Flat Block without Mounting Ears 节距:9.53 mm 位置/触点数量:2 线规量程:22-12 电流额定值:20 A 电压额定值:300 V 安装风格:Through Hole 安装角:Vertical 端接类型:Screw 触点电镀:Tin |

发布紧急采购,3分钟左右您将得到回复。