- 您现在的位置:买卖IC网 > PDF目录297617 > TSPC603PVG6ME 32-BIT, 166 MHz, RISC PROCESSOR, CBGA255 PDF资料下载

参数资料

| 型号: | TSPC603PVG6ME |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 166 MHz, RISC PROCESSOR, CBGA255 |

| 封装: | CBGA-255 |

| 文件页数: | 2/38页 |

| 文件大小: | 704K |

| 代理商: | TSPC603PVG6ME |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

TSPC603p

10/38

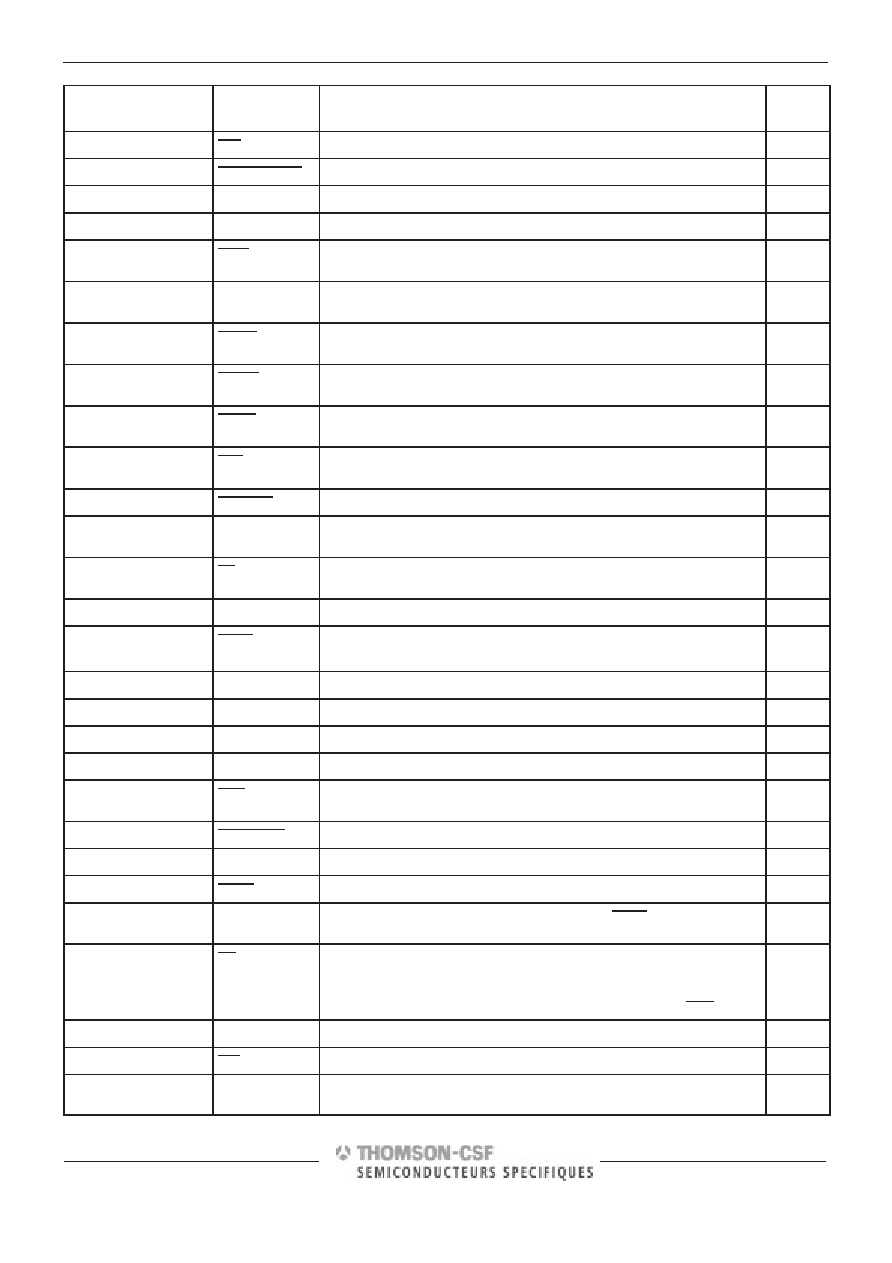

Signal name

Signal

type

Signal function

Mnemonic

Interrupt

INT

Initiates an interrupt if bit EE of MSR register is set

Input

LSSD_MODE

LSSD test control signal for factory use only

Input

L1_TSTCLK

LSSD test control signal for factory use only

Input

L2_TSTCLK

LSSD test control signal for factory use only

Input

Machine Check Inter-

rupt

MCP

Initiates a machine check interrupt operation if the bit ME of MSR regis-

ter and bit EMCP of HID0 register are set

Input

PLL Configuration

PLL_CFG[0-3]

Configures the operation of the PLL and the internal processor clock

frequency

Input

Quiescent

Acknowledge

QACK

All bus activity has terminated and the 603p may enter a quiescent (or

low power) state

Input

Quiescent Request

QREQ

Is requesting all bus activity normally to enter a quiescent (low power)

state

Output

Reservation

RSRV

Represents the state of the reservation coherency bit in the reservation

address register

Output

System Management

Interrupt

SMI

Initiates a system management interrupt operation if the bit EE of MSR

register is set

Input

Soft Reset

SRESET

Initiates processing for a reset exception

Input

System Clock

SYSCLK

Represents the primary clock input for the 603p, and the bus clock fre-

quency for 603p bus operation

Input

Transfer Acknowledge

TA

A single-beat data transfer completed successfully or a data beat in a

burst transfer completed successfully

Input

Timebase Enable

TBEN

The timebase should continue clocking

Input

Transfer Burst

TBST

If output, a burst transfer is in progress

If input, when snooping for single-beat reads

I/O

Transfer Code

TC[0-1]

Special encoding for the transfer in progress

Output

Test clock

TCK

Clock signal for the IEEE P1149.1 test access port (TAP)

Input

Test data input

TDI

Serial data input for the TAP

Input

Test data output

TDO

Serial data output for the TAP

Output

Transfer Error

Acknowledge

TEA

A bus error occurred

Input

TLBI Sync

TLBISYNC

Instruction execution should stop after execution of a tlbsync instruction

Input

Test mode select

TMS

Selects the principal operations of the test-support circuitry

Input

Test reset

TRST

Provides an asynchronous reset of the TAP controller

Input

Transfer Size

TSIZ[0-2]

For memory accesses, these signals along with TBST indicate the data

transfer size for the current bus operation

I/O

Transfer start

TS

If output, begun a memory bus transaction and the address bus and

transfer attribute signals are valid

If input, another master has begun a bus transaction and the address

bus and transfer attribute signals are valid for snooping (see GBL)

I/O

Transfer Type

TT[0-4]

Type of transfer in progress

I/O

Write-Through

WT

A single-beat transaction is write-through

Output

Power supply indicator

VOLTDETGND

Available only on BGA package

Indicates to the power supply that a low–voltage processor is present.

Output

相关PDF资料 |

PDF描述 |

|---|---|

| TSPC603PMGB/C8ME | 32-BIT, 200 MHz, RISC PROCESSOR, CBGA255 |

| TSPC603PMGB/C6ME | 32-BIT, 166 MHz, RISC PROCESSOR, CBGA255 |

| TSPC603PMGB/C6LE | 32-BIT, 166 MHz, RISC PROCESSOR, CBGA255 |

| TS(X)PC603PVGU/T8ME | 32-BIT, 200 MHz, RISC PROCESSOR, CBGA255 |

| TS(X)PC603PMGB/C6LE | 32-BIT, 166 MHz, RISC PROCESSOR, CBGA255 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSPC603R | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

| TSPC603RCAB/Q8L | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

| TSPC603RCAB/Q8LC | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

| TSPC603RMAB/Q8L | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

| TSPC603RMAB/Q8LC | 制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:PowerPC 603e RISC Microprocessor Family PID7t-603e |

发布紧急采购,3分钟左右您将得到回复。