- 您现在的位置:买卖IC网 > PDF目录98305 > TVP5010PFP (TEXAS INSTRUMENTS INC) COLOR SIGNAL DECODER, PQFP80 PDF资料下载

参数资料

| 型号: | TVP5010PFP |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 颜色信号转换 |

| 英文描述: | COLOR SIGNAL DECODER, PQFP80 |

| 封装: | POWERPAD, PLASTIC, TQFP-80 |

| 文件页数: | 2/59页 |

| 文件大小: | 250K |

| 代理商: | TVP5010PFP |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页

1–4

1.5

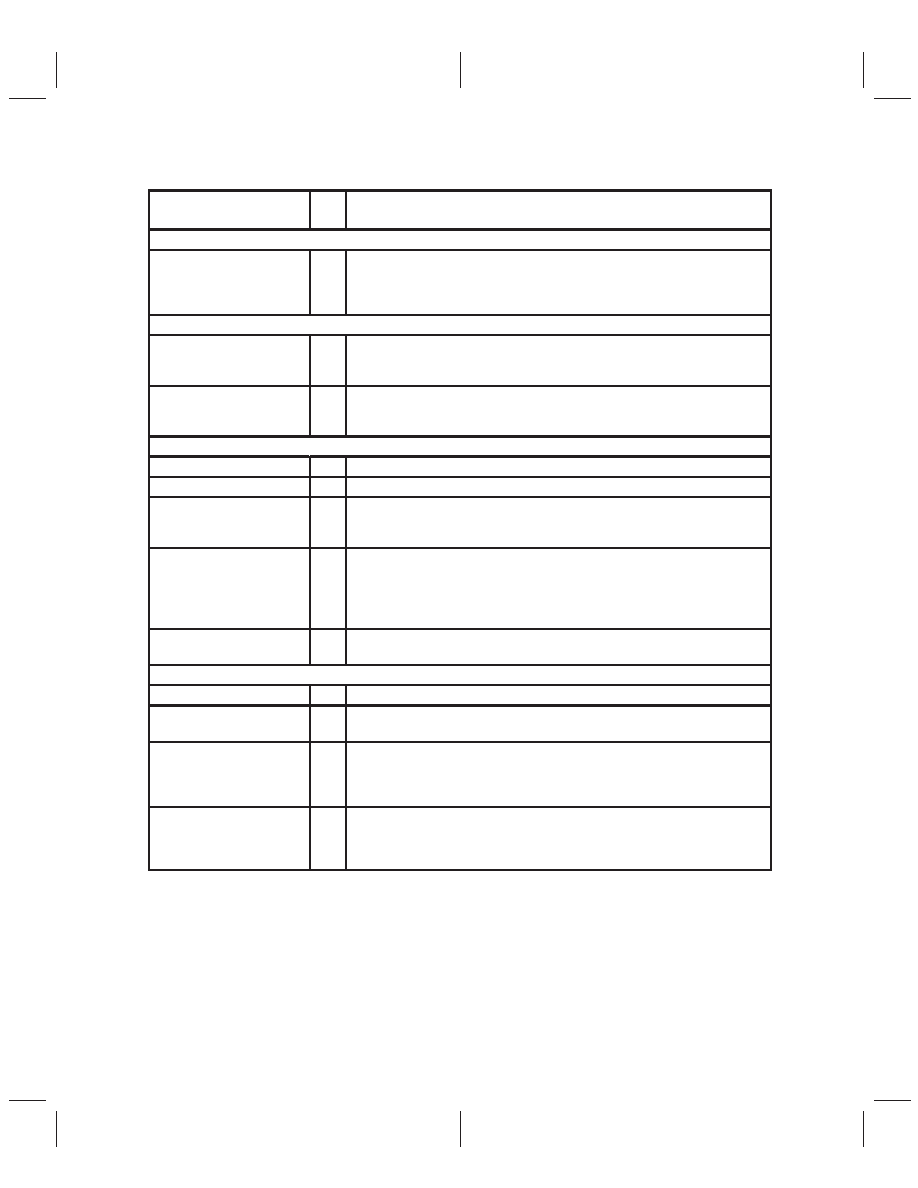

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

NO.

I/O

DESCRIPTION

Analog Video

VI1A

VI1B

VI2A

VI2B

2

80

6

8

I

Analog Video inputs. Up to four composite inputs or two S-video inputs or a

combination of the two. The inputs must be ac coupled. The recommended

coupling capacitor is 0.1

F.

Digital Video

Y[0:7]

37, 38, 39,

40, 43, 45,

46, 47

O

8-bit digital luminance outputs, or 8-bit multiplexed luminance and chrominance

outputs. These pins may also be configured to output data from the channel 1 A/D

converter.

UV[0:7]

48, 49, 50,

51, 53, 55,

56, 57

I/O

8-bit digital chrominance outputs. These pins may also be configured to output

data from the channel 2 A/D converter.

Clock Signals

LCLK

21

O

Clock output with one-half the frequency of the pixel clock (PCLK)

SCLK

22

O

System clock output with twice the frequency of the pixel clock (PCLK).

PCLK

23

O

Pixel clock output. The frequency is 12.2727 MHz for square-pixel NTSC,

14.75 MHz for square-pixel PAL, and 13.5 MHz for ITU-R BT.601 sampling

modes.

XTAL1

XTAL2

28

29

I

External clock reference. XTAL1 may be connected to a TTL-compatible

oscillator or to one terminal of a crystal oscillator. XTAL2 may be connected to

the second terminal of a crystal oscillator or left unconnected. The oscillator

frequencies used are 26.800 MHz for square pixel sampling or 24.576 MHz for

ITU-R BT.601 sampling.

PREF

24

O

Clock phase reference signal. This signal may be used to qualify clock edges

when SCLK is used to clock data which is changing at the pixel clock rate.

Sync Signals

HSYN

69

O

Horizontal sync signal. The rising edge time is programmable.

VSYN

63

O

Vertical sync or vertical blanking signal. The function of this pin is selected via

I2C control.

FID

65

O

Odd/even field indicator or vertical lock indicator. For odd/even indicator, a logic 1

indicates the odd field. For vertical lock indicator, a logic 1 indicates the internal

vertical processor is in locked state. The function of this pin is selected via I2C

control.

PALI

66

O

PAL line indicator or horizontal lock indicator. For PAL line indicator, a logic 1

indicates a noninverted line, and a logic 0 indicates an inverted line. For

horizontal lock indicator, a logic 1 indicates the internal horizontal PLL is in a

locked state. The function of this pin is selected via I2C control.

相关PDF资料 |

PDF描述 |

|---|---|

| TVP5020CPFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5020 | COLOR SIGNAL DECODER, PQFP80 |

| TVP5022 | COLOR SIGNAL DECODER, PQFP80 |

| TVP5031PFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5040CPFP | COLOR SIGNAL DECODER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TVP5020 | 制造商:TI 制造商全称:Texas Instruments 功能描述:NTSC/PAL VIDEO DECODER |

| TVP5020CPFP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TVP5020PFC | 制造商:未知厂家 制造商全称:未知厂家 功能描述: |

| TVP5020TQFP | 制造商:TI 制造商全称:Texas Instruments 功能描述:NTSC/PAL VIDEO DECODER |

| TVP5021PFP | 功能描述:视频 IC NTSC/PAL DIGITAL VIDEO DECODER RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。