- 您现在的位置:买卖IC网 > PDF目录98306 > TVP5158PNPR (TEXAS INSTRUMENTS INC) COLOR SIGNAL DECODER, PQFP128 PDF资料下载

参数资料

| 型号: | TVP5158PNPR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 颜色信号转换 |

| 英文描述: | COLOR SIGNAL DECODER, PQFP128 |

| 封装: | GREEN, PLASTIC, HTQFP-128 |

| 文件页数: | 41/108页 |

| 文件大小: | 1395K |

| 代理商: | TVP5158PNPR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

SLES243E

– JULY 2009 – REVISED MARCH 2011

3.10.1 I

2C Write Operation

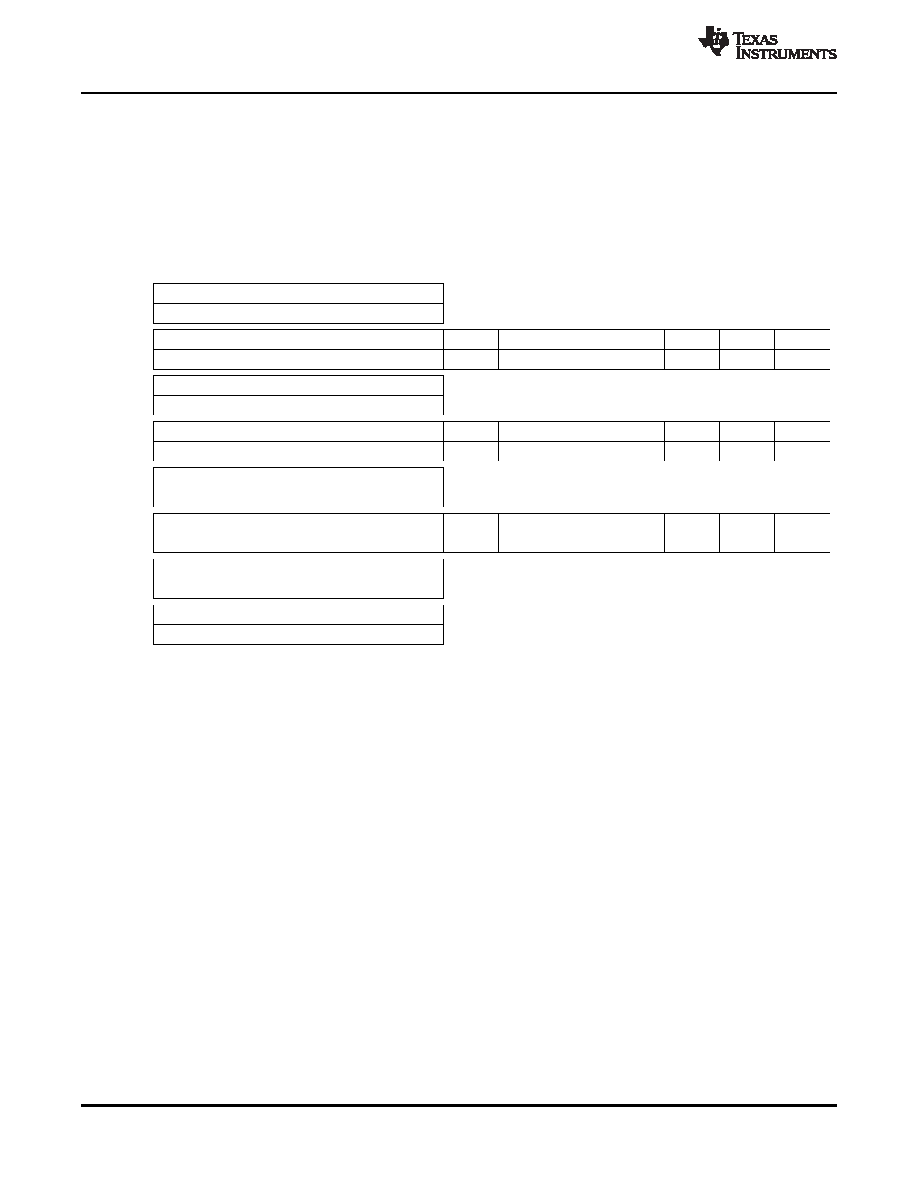

Data transfers occur utilizing the following formats.

An I2C master initiates a write operation to the decoder by generating a start condition (S) followed by the

decoder I2C address (as shown below), in MSB first bit order, followed by a 0 to indicate a write cycle.

After receiving an acknowledge from the decoder, the master presents the sub-address of the register, or

the first of a block of registers it wants to write, followed by one or more bytes of data, MSB first. The

decoder acknowledges each byte after completion of each transfer. The I2C master terminates the write

operation by generating a stop condition (P).

Step 1

0

I2C Start (master)

S

Step 2

7

6

5

4

3

2

1

0

I2C General address (master)

1

0

1

0

X

0

Step 3

9

I2C Acknowledge (slave)

A

Step 4

7

6

5

4

3

2

1

0

I2C Write register address (master)

Addr

Step 5

9

I2C Acknowledge (slave)

A

Step 6(1)

7

6

5

4

3

2

1

0

I2C Write data (master)

Data

Step 7(1)

9

I2C Acknowledge (slave)

A

Step 8

0

I2C Stop (master)

P

(1)

Repeat steps 6 and 7 until all data have been written.

3.10.2 I

2C Read Operation

The read operation consists of two phases. The first phase is the address phase. In this phase, an I2C

master initiates a write operation to the decoder by generating a start condition (S) followed by the

decoder slave address, in MSB first bit order, followed by a 0 to indicate a write cycle. After receiving

acknowledge from the decoder, the master presents the sub-address of the register or the first of a block

of registers it wants to read. After the cycle is acknowledged, the master has the option of generating a

stop condition or not.

In the data phase, an I2C master initiates a read operation to the decoder by generating a start condition

followed by the decoder I2C slave address (as shown below for a read operation), in MSB first bit order,

followed by a 1 to indicate a read cycle. After an acknowledge from the decoder, the I2C master receives

one or more bytes of data from the decoder. The I2C master acknowledges the transfer at the end of each

byte. After the last data byte has been transferred from the decoder, the master generates a not

acknowledge followed by a stop.

38

Functional Description

Copyright

2009–2011, Texas Instruments Incorporated

相关PDF资料 |

PDF描述 |

|---|---|

| TVP5158PNP | COLOR SIGNAL DECODER, PQFP128 |

| TVP5160PNPG4 | COLOR SIGNAL DECODER, PQFP128 |

| TVP5160PNP | COLOR SIGNAL DECODER, PQFP128 |

| TVP5200PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TVP6000CPFP | COLOR SIGNAL ENCODER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TVP5160 | 制造商:Texas Instruments 功能描述:2x10-bit Video Decoder TVP5160 |

| TVP5160_11 | 制造商:TI 制造商全称:Texas Instruments 功能描述:NTSC/PAL/SECAM/Component 2x10-Bit Digital Video Decoder |

| TVP5160EVM | 功能描述:视频 IC 开发工具 TVP5160 Eval Mod RoHS:否 制造商:Texas Instruments 产品:Evaluation Boards 类型:YPbPr to RGBHV Converters 工具用于评估:LMH1251 工作电源电压:5 V |

| TVP5160PNP | 功能描述:视频 IC NTSC/PAL/SECAM/Comp 10B Dig Vid Decoder RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

| TVP5160PNPG4 | 制造商:Texas Instruments 功能描述: |

发布紧急采购,3分钟左右您将得到回复。