- 您现在的位置:买卖IC网 > PDF目录202171 > V53C8125HT50 (MOSEL-VITELIC) 128K X 8 FAST PAGE DRAM, 50 ns, PDSO28 PDF资料下载

参数资料

| 型号: | V53C8125HT50 |

| 厂商: | MOSEL-VITELIC |

| 元件分类: | DRAM |

| 英文描述: | 128K X 8 FAST PAGE DRAM, 50 ns, PDSO28 |

| 封装: | TSOP1-28 |

| 文件页数: | 7/17页 |

| 文件大小: | 1527K |

| 代理商: | V53C8125HT50 |

MOSEL VITELIC

V53C8125H

15

V53C8125H Rev. 1.7 August 1998

Fast Page Mode provides sustained data rates

up to 53 MHz for applications that require high data

rates such as bit-mapped graphics or high-speed

signal processing. The following equation can be

used to calculate the maximum data rate:

Data Output Operation

The V53C8125H Input/Output is controlled by

OE, CAS, WE and RAS. A RAS low transition en-

ables the transfer of data to and from the selected

row address in the Memory Array. A RAS high tran-

sition disables data transfer and latches the output

data if the output is enabled. After a memory cycle

is initiated with a RAS low transition, a CAS low

transition or CAS low level enables the internal I/O

path. A CAS high transition or a CAS high level dis-

ables the I/O path and the output driver if it is en-

abled. A CAS low transition while RAS is high has

no effect on the I/O data path or on the output driv-

ers. The output drivers, when otherwise enabled,

can be disabled by holding OE high. The OE signal

has no effect on any data stored in the output latch-

es. A WE low level can also disable the output driv-

ers when CAS is low. During a Write cycle, if WE

goes low at a time in relationship to CAS that would

normally cause the outputs to be active, it is neces-

sary to use OE to disable the output drivers prior to

the WE low transition to allow Data In Setup Time

(tDS) to be satisfied.

Power-On

After application of the VCC supply, an initial

pause of 200

s is required followed by a minimum

of 8 initialization cycles (any combination of cycles

containing a RAS clock). Eight initialization cycles

are required after extended periods of bias without

clocks (greater than the Refresh Interval).

During Power-On, the VCC current requirement of

the V53C8125H is dependent on the input levels of

RAS and CAS. If RAS is low during Power-On, the

device will go into an active cycle and IDD will exhibit

current transients. It is recommended that RAS and

CAS track with VCC or be held at a valid VIH during

Power-On to avoid current surges.

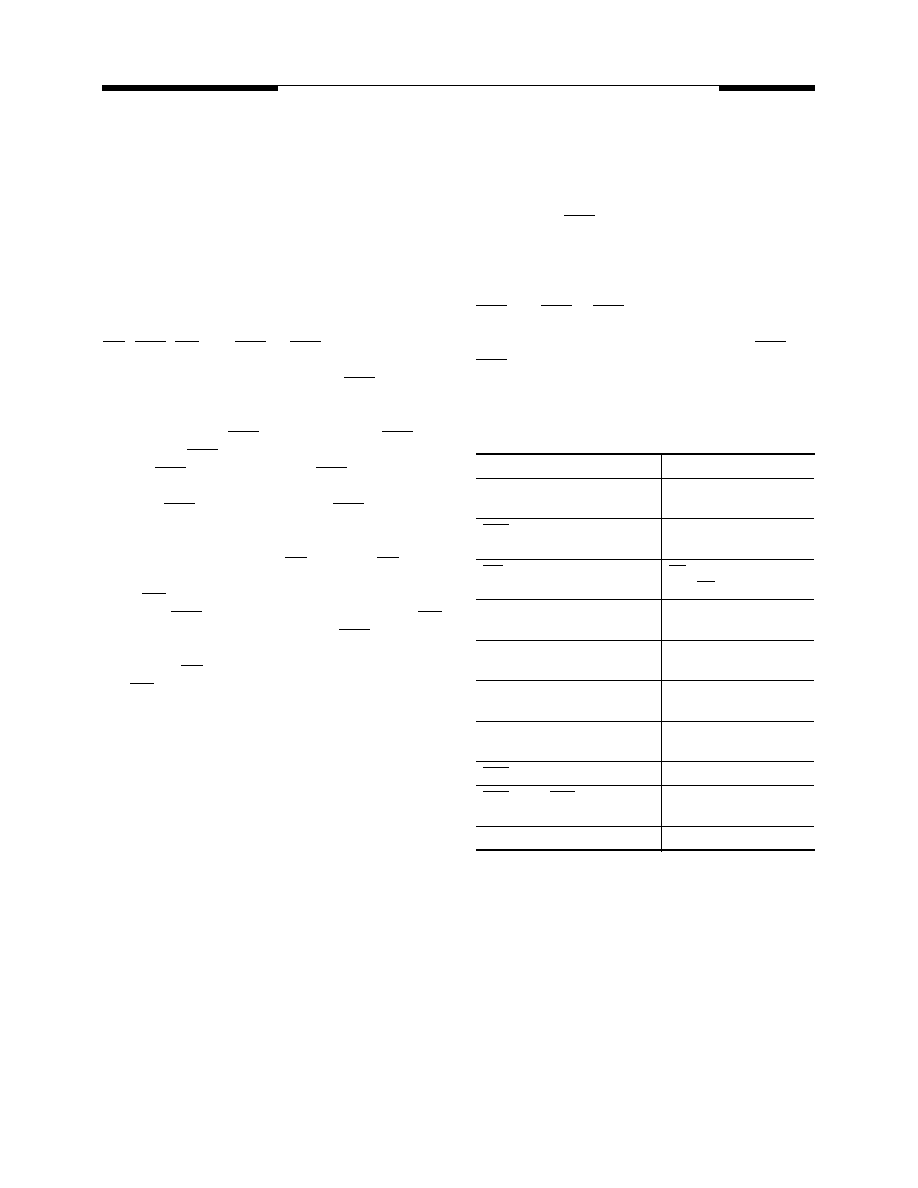

Table 1. V53C8125H Data Output

Operation for Various Cycle Types

Data Rate

256

t

RC

255

t

PC

×

+

----------------------------------------

=

Cycle Type

I/O State

Read Cycles

Data from Addressed

Memory Cell

CAS-Controlled Write

Cycle (Early Write)

High-Z

WE-Controlled Write

Cycle (Late Write)

OE Controlled.

High OE = High-Z I/Os

Read-Modify-Write

Cycles

Data from Addressed

Memory Cell

Fast Page Mode

Read

Data from Addressed

Memory Cell

Fast Page Mode Write

Cycle (Early Write)

High-Z

Fast Page Mode Read-Modify-

Write Cycle

Data from Addressed

Memory Cell

RAS-only Refresh

High-Z

CAS-before-RAS

Refresh Cycle

Data remains as in

previous cycle

CAS-only Cycles

High-Z

相关PDF资料 |

PDF描述 |

|---|---|

| V53C8125LK60LE | 128K X 8 FAST PAGE DRAM, 60 ns, PDSO24 |

| V54C3128404VBI6I | 32M X 4 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| V54C3128404VBJ8PC | 32M X 4 SYNCHRONOUS DRAM, 6 ns, PBGA60 |

| V54C3128804VBLT7 | 16M X 8 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| V54C3128804VBT7PC | 16M X 8 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V53C8256HP45 | 制造商:Mosel Vitelic Corporation 功能描述: |

| V53C864K10L | 制造商:VITELIC 功能描述: |

| V53C864K80L | 制造商:VITELIC 功能描述: |

| V5-4/RK 4-0.3/0.3/0.3 | 制造商:TURCK Inc 功能描述:Cordset, Splitter, M12 Female Straight x 3, 4 Wire, 4m, PVC, Yellow |

| V-5410EK | 制造商:Honeywell Sensing and Control 功能描述:V Basics |

发布紧急采购,3分钟左右您将得到回复。