- 您现在的位置:买卖IC网 > PDF目录361765 > W127 Clocks and Buffers PDF资料下载

参数资料

| 型号: | W127 |

| 英文描述: | Clocks and Buffers |

| 中文描述: | 时钟和缓冲器 |

| 文件页数: | 3/20页 |

| 文件大小: | 200K |

| 代理商: | W127 |

W127/W127-A

PRELIMINARY

Document #: 38-07225 Rev. *A

Page 3 of 20

W127/W127-A Pin Selection Tables

Overview

The W127/W127-A was designed specifically to provide all

clock signals required for a motherboard designed with the Via

MVP3 chipset using either a Pentium

or K6 microprocessor.

Although it can be used with split voltages (3.3/2.5), the skew

specifications are guaranteed only for single 3.3V supply. The

primary distinguishing feature of the W127/W127-A is the

95.25-MHz CPU frequency option, which supports the K6 333-

MHz CPU.

Twelve SDRAM outputs are provided for support of up to 3

SDRAM DIMM modules. Unused clock outputs can be dis-

abled through the I

2

C interface to reduce system power con-

sumption and more importantly reduce EMI emissions.

Functional Description

I/O Pin Operation

Pins 3, 8, 17, 47, and 48 are dual-purpose l/O pins. Upon

power-up these pins act as logic inputs, allowing the determi-

nation of assigned device functions. A short time after power-

up, the logic state of each pin is latched and the pins then

become clock outputs. This feature reduces device pin count

by combining clock outputs with input select pins.

An external 10-k

“

strapping

”

resistor is connected between

each l/O pin and ground or V

DDQ3

. Connection to ground sets

a latch to

“

0,

”

connection to V

DDQ3

sets a latch to

“

1.

”

Figure 1

and

Figure 2

show two suggested methods for strapping resis-

tor connection.

Upon W127/W127-A power-up, the first 2 ms of operation is

used for input logic selection. During this period, the 24-MHz,

48-MHz, REF, PCI_F and AGP_F clock output buffers are

three-stated, allowing the output strapping resistor on each l/O

pin to pull the pin and its associated capacitive clock load to

either a logic HIGH or logic LOW state. At the end of the 2-ms

period, the established logic 0 or 1 condition of each l/O pin is

latched. Next the output buffers are enabled, converting all l/O

pins into operating clock outputs. The 2-ms timer starts when

V

DDQ3

reaches 2.0V. The input bits can only be reset by turn-

ing V

DDQ3

off and then back on again.

It should be noted that the strapping resistors have no signifi-

cant effect on clock output signal integrity. The drive imped-

ance of the clock output is 40

(nominal), which is minimally

affected by the 10-k

strap to ground or V

DDQ3

. As with the

series termination resistor, the output strapping resistor should

be placed as close to the l/O pin as possible in order to keep

the interconnecting trace short. The trace from the resistor to

ground or V

DDQ3

should be kept less than two inches in length

to prevent system noise coupling during input logic sampling.

When the clock outputs are enabled following the 2-ms input

period, target (normal) output frequency is delivered, assum-

ing that V

DDQ3

has stabilized. If V

DDQ3

has not yet reached full

value, output frequency initially may be below target but will

increase to target once V

DDQ3

voltage has stabilized. In either

case, a short output clock cycle may be produced from the

CPU clock outputs when the outputs are enabled.

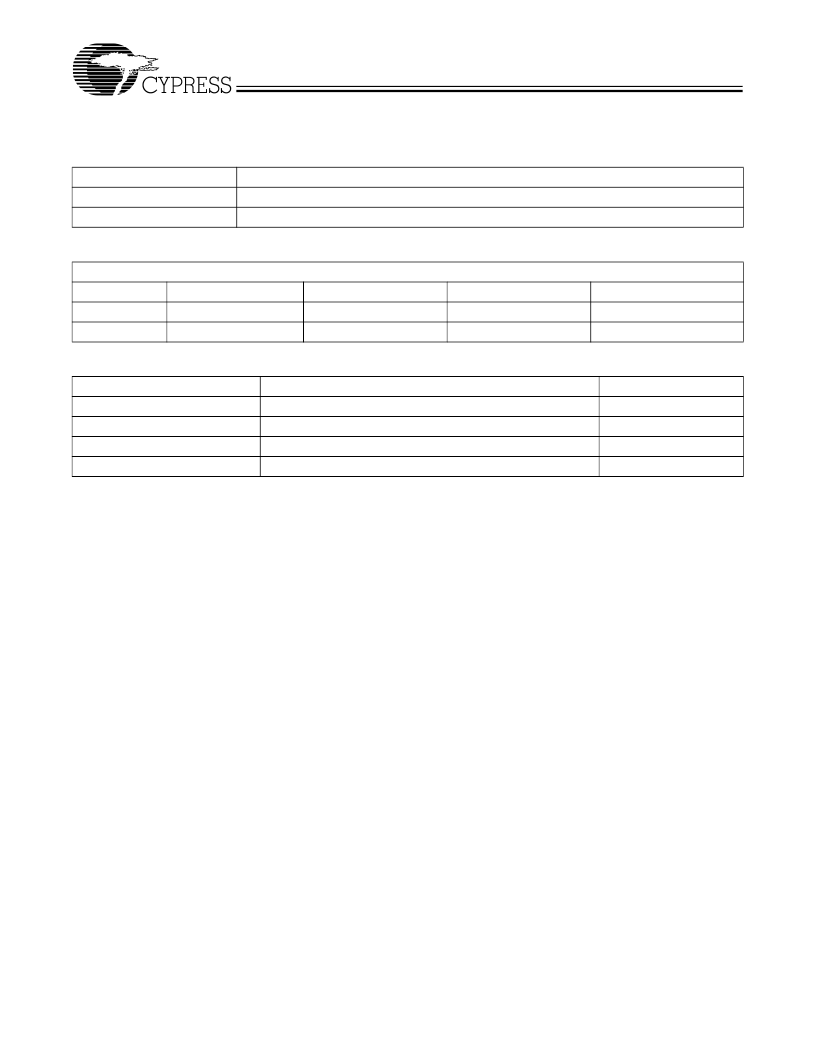

Table 2. SD_SEL Function

SD_SEL

1

0

SDRAM0:11

Running @ CPU Frequency

Running @ AGP Frequency

Table 3. Mode Function

Pin Function

Pin 30

SDRAM6

CPU_STOP#

Mode

1

0

Pin 29

SDRAM7

PCI_STOP#

Pin 31

SDRAM5

PWR_DWN#

Pin 32

SDRAM4

AGP_STOP#

Table 4. Power Management Pin Function

SIGNAL

CPU_STOP#

PCI_STOP#

AGP_STOP#

PWR_DWN#

=0

=1

CPU0:3 & SDRAM0:11 = LOW

PCI0:4 = LOW

AGP0 = LOW

All Clock Outputs LOW

Active

Active

Active

Active

相关PDF资料 |

PDF描述 |

|---|---|

| W132-09BX | Nine Distributed-Output Clock Driver |

| W132-10B | Ten Distributed-Output Clock Driver |

| W132-10BX | Ten Distributed-Output Clock Driver |

| W132-09B | Nine Distributed-Output Clock Driver |

| W134MH | Miscellaneous Clock Generator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W1-270 | 制造商:HellermannTyton 功能描述:CABLE MARKER COLOUR 0.5-1.5MM 制造商:HellermannTyton 功能描述:CABLE MARKER, COLOUR, 0.5-1.5MM 制造商:HELLERMANN TYTON 功能描述:CABLE MARKER, CLIP ON, 0-TO-9, 200PC; Cable Diameter Min:2mm; Cable Diameter Max:2.8mm; Legend:0 to 9; Legend Color:Black, White; Marker Material:Polyimide; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No ;RoHS Compliant: Yes |

| W1-272 | 制造商:HellermannTyton 功能描述:CABLE MARKER BLACK/YELLOW 0.5-1.5MM 制造商:HellermannTyton 功能描述:CABLE MARKER, BLACK/YELLOW, 0.5-1.5MM 制造商:HELLERMANN TYTON 功能描述:CABLE MARKER, BLACK/YELLOW, 0.5-1.5MM; Cable Diameter Min:2.0mm; Cable Diameter Max:2.8mm; Legend:A,E,L,N,R,S,T,+,-,Earth; Marker Colour:Yellow; Marker Material:Nylon 6.6 (Polyamide 6.6); SVHC:No SVHC (19-Dec-2012); Accessory ;RoHS Compliant: Yes |

| W127E13C | 制造商:OMRON INDUSTRIAL AUTOMATION 功能描述:C200H Analog I/O Unit Manual DX CODE ZA |

| W1280 | 制造商:LUMINIS 制造商全称:LUMINIS 功能描述:Wall mount |

| W1282 | 制造商:LUMINIS 制造商全称:LUMINIS 功能描述:Wall mount |

发布紧急采购,3分钟左右您将得到回复。