- 您现在的位置:买卖IC网 > PDF目录361765 > W132-09BX Nine Distributed-Output Clock Driver PDF资料下载

参数资料

| 型号: | W132-09BX |

| 英文描述: | Nine Distributed-Output Clock Driver |

| 中文描述: | 九分布式输出时钟驱动器 |

| 文件页数: | 3/13页 |

| 文件大小: | 151K |

| 代理商: | W132-09BX |

W134M/W134S

Document #: 38-07426 Rev. *A

Page 3 of 13

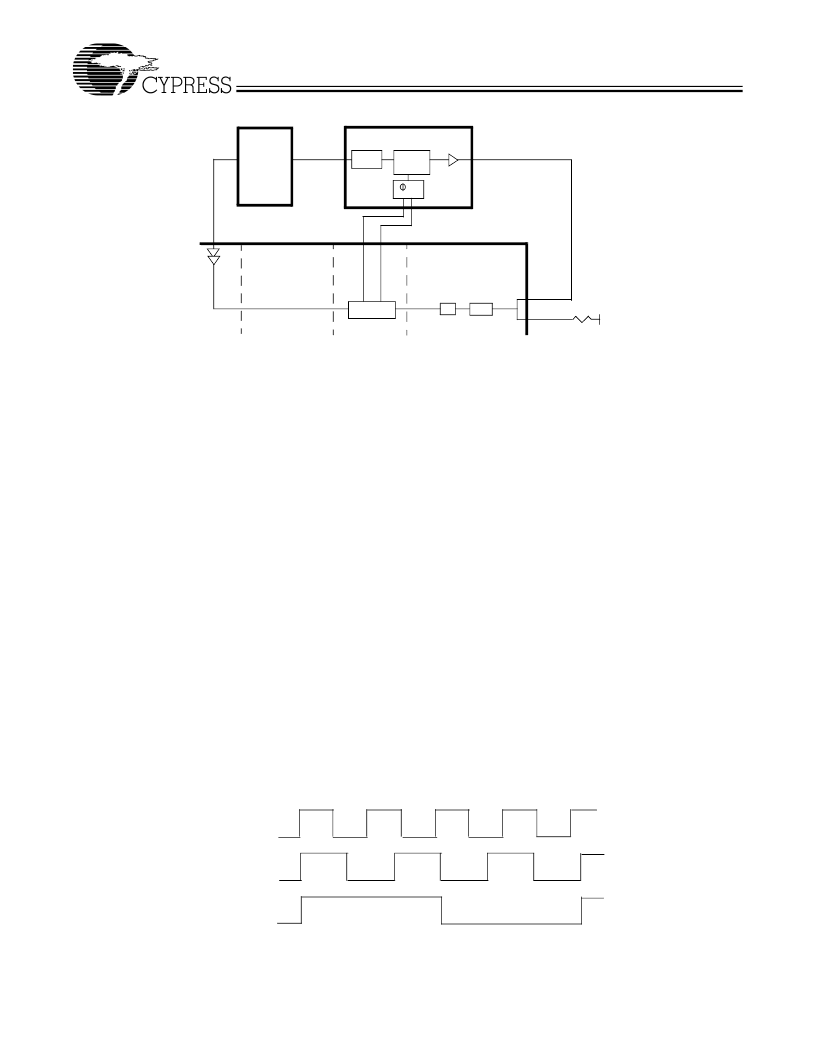

DDLL System Architecture and Gear Ratio Log-

ic

Figure 1

shows the Distributed Delay Lock Loop (DDLL) sys-

tem architecture, including the main system clock source, the

Direct Rambus clock generator (DRCG), and the core logic

that contains the Rambus Access Cell (RAC), the Rambus

Memory Controller (RMC), and the Gear Ratio Logic. (This

diagram abstractly represents the differential clocks as a sin-

gle Busclk wire.)

The purpose of the DDLL is to frequency-lock and phase-align

the core logic and Rambus clocks (Pclk and Synclk) at the

RMC/RAC boundary in order to allow data transfers without

incurring additional latency. In the DDLL architecture, a PLL is

used to generate the desired Busclk frequency, while a distrib-

uted loop forms a DLL to align the phase of Pclk and Synclk at

the RMC/RAC boundary.

The main clock source drives the system clock (Pclk) to the

core logic, and also drives the reference clock (Refclk) to the

DRCG. For typical Intel architecture platforms, Refclk will be

half the CPU front side bus frequency. A PLL inside the DRCG

multiplies Refclk to generate the desired frequency for Busclk,

and Busclk is driven through a terminated transmission line

(Rambus Channel). At the mid-point of the channel, the RAC

senses Busclk using its own DLL for clock alignment, followed

by a fixed divide-by-4 that generates Synclk.

Pclk is the clock used in the memory controller (RMC) in the

core logic, and Synclk is the clock used at the core logic inter-

face of the RAC. The DDLL together with the Gear Ratio Logic

enables users to exchange data directly from the Pclk domain

to the Synclk domain without incurring additional latency for

synchronization. In general, Pclk and Synclk can be of differ-

ent frequencies, so the Gear Ratio Logic must select the ap-

propriate M and N dividers such that the frequencies of Pclk/M

and Synclk/N are equal. In one interesting example,

Pclk = 133 MHz, Synclk = 100 MHz, and M = 4 while N = 3,

giving Pclk/M = Synclk/N = 33 MHz. This example of the clock

waveforms with the Gear Ratio Logic is shown in

Figure 2

.

The output clocks from the Gear Ratio Logic, Pclk/M, and

Synclk/N, are output from the core logic and routed to the

DRCG Phase Detector inputs. The routing of Pclk/M and Syn-

clk/N must be matched in the core logic as well as on the

board.

After comparing the phase of Pclk/M vs. Synclk/N, the DRCG

Phase Detector drives a phase aligner that adjusts the phase

of the DRCG output clock, Busclk. Since everything else in the

distributed loop is fixed delay, adjusting Busclk adjusts the

phase of Synclk and thus the phase of Synclk/N. In this man-

ner the distributed loop adjusts the phase of Synclk/N to match

that of Pclk/M, nulling the phase error at the input of the DRCG

Phase Detector. When the clocks are aligned, data can be

exchanged directly from the Pclk domain to the Synclk do-

main.

Table 1

shows the combinations of Pclk and Busclk frequen-

cies of greatest interest, organized by Gear Ratio.

W134M/W134S

Refclk

W133

W158

W159

W161

W167

CY2210

PLL

Phase

Align

D

4

DLL

RAC

RMC

M N

Gear

Ratio

Logic

Pclk

Busclk

Synclk

P

S

Figure 1. DDLL System Architecture

Pclk

Synclk

Pclk/M =

Synclk/N

Figure 2. Gear Ratio Timing Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| W132-10B | Ten Distributed-Output Clock Driver |

| W132-10BX | Ten Distributed-Output Clock Driver |

| W132-09B | Nine Distributed-Output Clock Driver |

| W134MH | Miscellaneous Clock Generator |

| W134M | Direct Rambus Clock Generator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W132-09BXT | 制造商:Cypress Semiconductor 功能描述:SPREAD AWARE ZERO DELAY BUFFER |

| W132-10B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Ten Distributed-Output Clock Driver |

| W132-10BX | 制造商:Cypress Semiconductor 功能描述:Zero Delay PLL Clock Buffer Single 25MHz to 140MHz 24-Pin TSSOP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| W132-10BXT | 制造商:Cypress Semiconductor 功能描述:Zero Delay PLL Clock Buffer Single 25MHz to 140MHz 24-Pin TSSOP T/R 制造商:Rochester Electronics LLC 功能描述:CLK DRIVER - Tape and Reel |

| W132E13B | 制造商:OMRON INDUSTRIAL AUTOMATION 功能描述:Discontinued |

发布紧急采购,3分钟左右您将得到回复。