- 您现在的位置:买卖IC网 > PDF目录361765 > W132-09BX Nine Distributed-Output Clock Driver PDF资料下载

参数资料

| 型号: | W132-09BX |

| 英文描述: | Nine Distributed-Output Clock Driver |

| 中文描述: | 九分布式输出时钟驱动器 |

| 文件页数: | 7/13页 |

| 文件大小: | 151K |

| 代理商: | W132-09BX |

W134M/W134S

Document #: 38-07426 Rev. *A

Page 7 of 13

Figure 5

shows that the Clk Stop to Normal transition goes

through three phases. During t

CLKON

, the clock output is not

specified and can have glitches. For t

CLKON

< t < t

CLKSETL

, the

clock output is enabled and must be glitch-free. For

t > t

CLKSETL

, the clock output phase must be settled to within

50 ps of the phase before the clock output was disabled. At

this time, the clock output must also meet the voltage and tim-

ing specifications of

Table 14

. The outputs are in a high-imped-

ance state during the Clk Stop mode.

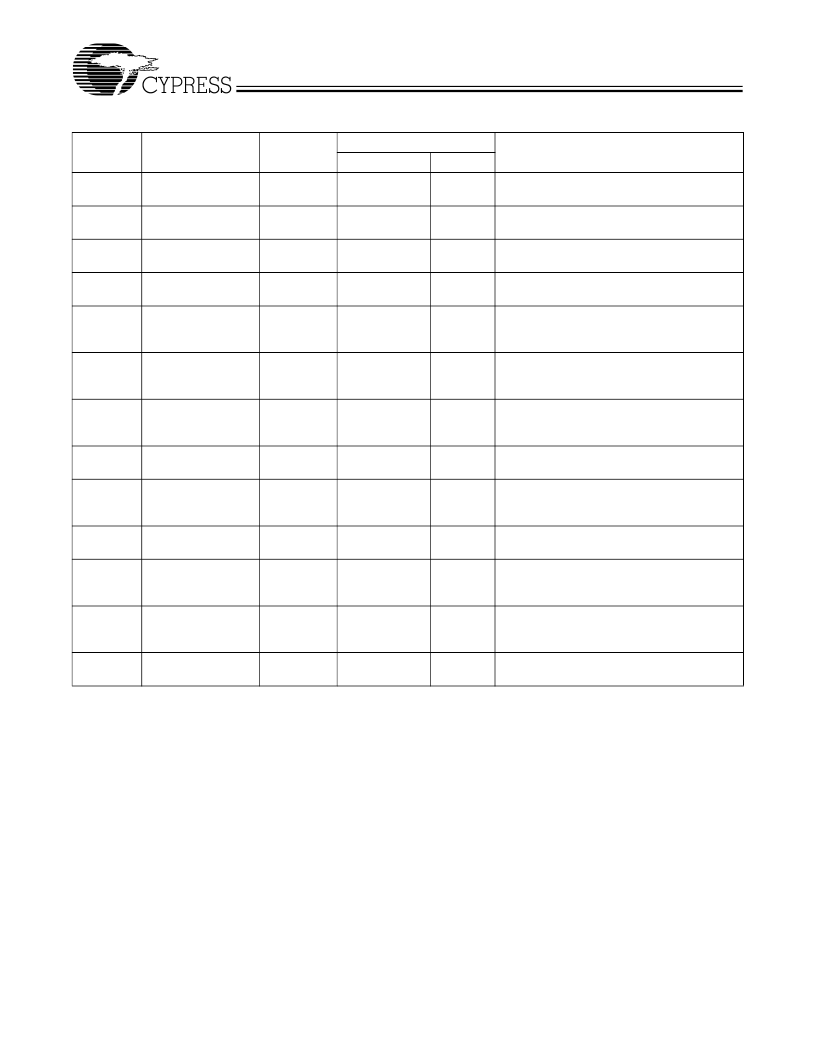

Table 8. State Transition Latency Specifications

Transition

A

From

To

Transition Latency

Symbol

t

POWERUP

Description

Max.

3 ms

Power-down

Normal

Time from PwrDnB to Clk/ClkB output settled

(excluding t

DISTLOCK

).

Time from PwrDnB until the internal PLL and

clock has turned ON and settled.

Time from PwrDnB to Clk/ClkB output settled

(excluding t

DISTLOCK

).

Time from V

DD

is applied and settled until

Clk/ClkB output settled (excluding t

DISTLOCK

).

Time from V

DD

is applied and settled until

internal PLL and clock has turned ON and

settled.

Time from V

DD

is applied and settled until

internal PLL and clock has turned ON and

settled.

Time from when Mult0 or Mult1 changed until

Clk/ClkB output resettled (excluding

t

DISTLOCK

).

Time from StopB until Clk/ClkB provides

glitch-free clock edges.

Time from StopB to Clk/ClkB output settled to

within 50 ps of the phase before CLK/CLKB

was disabled.

Time from StopB

Φ

to Clk/ClkB output

disabled.

Time from when S0 or S1 is changed until

CLK/CLKB output has resettled (excluding

t

DISTLOCK

).

Time from when S0 or S1 is changed until

CLK/CLKB output has resettled (excluding

t

DISTLOCK

).

Time from PwrDnB

Φ

to the device in Power-

down.

C

Power-down

Clk Stop

t

POWERUP

3 ms

K

Power-down

Test

t

POWERUP

3 ms

G

V

DD

ON

Normal

t

POWERUP

3 ms

H

V

DD

ON

Clk Stop

t

POWERUP

3 ms

M

V

DD

ON

Test

t

POWERUP

3 ms

J

Normal

Normal

t

MULT

1 ms

E

Clk Stop

Normal

t

CLKON

10 ns

E

Clk Stop

Normal

t

CLKSETL

20 cycles

F

Normal

Clk Stop

t

CLKOFF

5 ns

L

Test

Normal

t

CTL

3 ms

N

Normal

Test

t

CTL

3 ms

B,D

Normal or Clk Stop

Power-down

t

POWERDN

1 ms

相关PDF资料 |

PDF描述 |

|---|---|

| W132-10B | Ten Distributed-Output Clock Driver |

| W132-10BX | Ten Distributed-Output Clock Driver |

| W132-09B | Nine Distributed-Output Clock Driver |

| W134MH | Miscellaneous Clock Generator |

| W134M | Direct Rambus Clock Generator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W132-09BXT | 制造商:Cypress Semiconductor 功能描述:SPREAD AWARE ZERO DELAY BUFFER |

| W132-10B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Ten Distributed-Output Clock Driver |

| W132-10BX | 制造商:Cypress Semiconductor 功能描述:Zero Delay PLL Clock Buffer Single 25MHz to 140MHz 24-Pin TSSOP 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| W132-10BXT | 制造商:Cypress Semiconductor 功能描述:Zero Delay PLL Clock Buffer Single 25MHz to 140MHz 24-Pin TSSOP T/R 制造商:Rochester Electronics LLC 功能描述:CLK DRIVER - Tape and Reel |

| W132E13B | 制造商:OMRON INDUSTRIAL AUTOMATION 功能描述:Discontinued |

发布紧急采购,3分钟左右您将得到回复。