- 您现在的位置:买卖IC网 > PDF目录361766 > W195 Clocks and Buffers PDF资料下载

参数资料

| 型号: | W195 |

| 英文描述: | Clocks and Buffers |

| 中文描述: | 时钟和缓冲器 |

| 文件页数: | 1/14页 |

| 文件大小: | 142K |

| 代理商: | W195 |

PRELIMINARY

Frequency Generator for Integrated Core Logic

W195B

Cypress Semiconductor Corporation

Document #: 38-07160 Rev. *A

3901 North First Street

San Jose

CA 95134

408-943-2600

Revised December 14, 02

Features

Maximized EMI suppression using Cypress’s Spread

Spectrum Technology

Low jitter and tightly controlled clock skew

Highly integrated device providing clocks required for

CPU, core logic, and SDRAM

Two copies of CPU clocks

Nine copies of SDRAM clocks

Eight copies of PCI clock

One copy of synchronous APIC clock

Two copies of 66-MHz outputs

Two copies of 48-MHz outputs

One copy of selectable 24- or 48-MHz clock

One copy of double strength 14.31818-MHz reference

clock

Power-down control

I

2

C interface for turning off unused clocks

Key Specifications

CPU, SDRAM Outputs Cycle-to-Cycle Jitter: ............. 250 ps

APIC, 48 MHz, 3V66, PCI Outputs

Cycle-to-Cycle Jitter: .................................................. 500 ps

CPU, 3V66 Output Skew: .......................................... 175 ps

SDRAM, APIC, 48MHz Output Skew: ........................250 ps

PCI Output Skew:........................................................500 ps

CPU to SDRAM Skew (@100 MHz):..................4.5 to 5.5 ns

CPU to 3V66 Skew (@ 66 MHz): .......................7.0 to 8.0 ns

3V66 to PCI Skew (3V66 lead):..........................1.5 to 3.5 ns

PCI to APIC Skew: ....................................................

± 0.5 ns

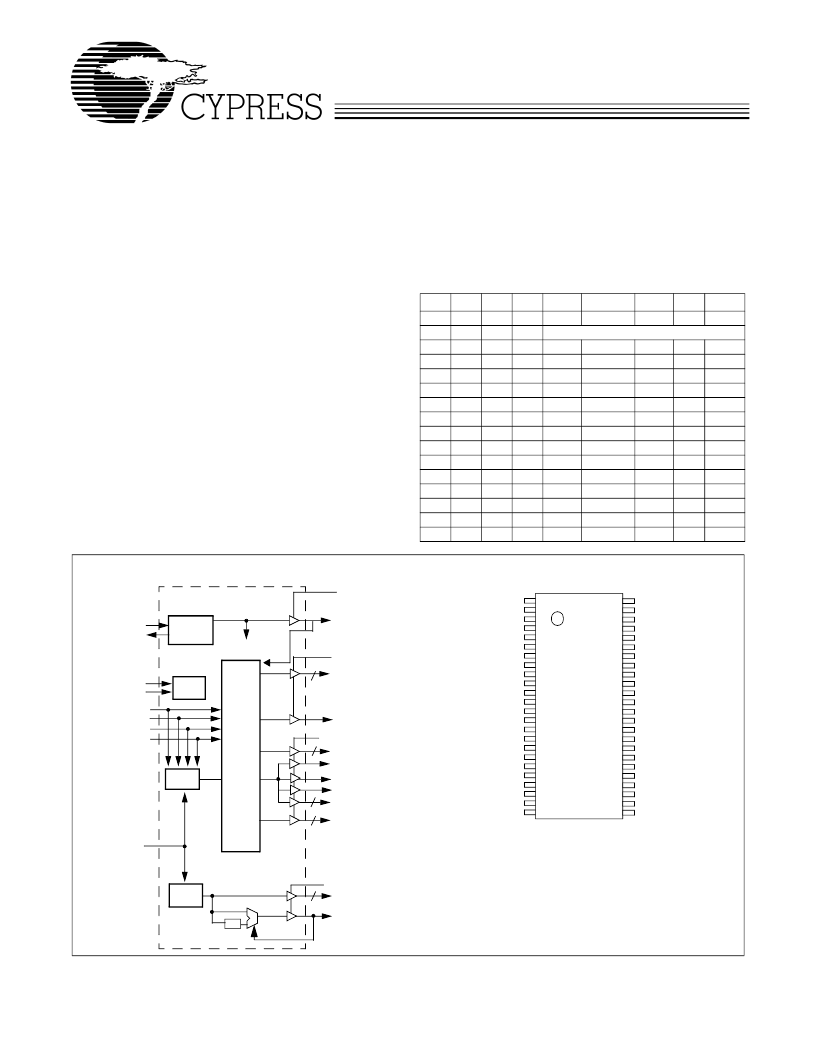

Table 1. Frequency Selections

FS3 FS2 FS1 FS0

CPU

1

1

1

1

133.6

1

1

1

0

1

1

0

1

100.2

1

1

0

0

66.8

1

0

1

1

105

1

0

1

0

110

1

0

0

1

114

1

0

0

0

119

0

1

1

1

124

0

1

1

0

129

0

1

0

1

95

0

1

0

0

138

0

0

1

1

150

0

0

1

0

75

0

0

0

1

90

0

0

0

0

83.3

SDRAM 3V66

133.6

Reserved

100.2

100.2

105

110

114

119

124

129

95

138

150

113

90

125

PCI

33.4

APIC

16.7

66.8

66.8

66.8

70

73.3

76

79.3

82.7

64.5

63.3

69

75

75

60

83.3

33.4

33.4

35

36.7

38

39.7

41.3

32.3

31.7

34.5

37.5

37.5

30

41.7

16.7

16.7

17.5

18.3

19

19.8

20.7

16.1

15.8

17.3

18.8

18.8

15

20.8

Block Diagram

Pin Configuration

VDDQ3

VDDQ2

PCI1/FS1*

PCI2/FS2*

XTAL

OSC

PLL REF FREQ

PLL 1

X2

X1

REF2X/FS3*

PCI3:7

48MHz_0:1

SI0/24_48#MHz*

PLL2

VDDQ3

I

2

C

Logic

SDATA

SCLK

3V66_0:1

PCI0/FS0*

CPU0:1

APIC

Divider,

Delay,

and

Phase

Control

Logic

2

VDDQ3

2

SDRAM0:8

9

PWRDWN#

/2

FS3*

FS2*

FS1*

FS0*

5

2

REF2x/FS3*

VDDQ3

X1

X2

GND

VDDQ3

3V66_0

3V66_1

GND

FS0*/PCI0

FS1^/PCI1

FS2*/PCI2

GND

PCI3

PCI4

VDDQ3

PCI5

PCI6

PCI7

GND

48MHz_0

48MHz_1

SI0/24_48#MHz*

VDDQ3

W

VDDQ2

APIC

VDDQ2

CPU0

CPU1

GND

VDDQ3

SDRAM0

SDRAM1

SDRAM2

GND

SDRAM3

SDRAM4

SDRAM5

VDDQ3

SDRAM6

SDRAM7

SDRAM8

GND

PWRDWN#*

SCLK

VDDQ3

GND

SDATA

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Note:

1.

Internal 250K pull-up or pull down resistors present on inputs

marked with * or ^ respectively. Design should not rely solely on

internal pull-up or pull down resistor to set I/O pins HIGH or LOW

respectively.

[1]

相关PDF资料 |

PDF描述 |

|---|---|

| W2005ABE | FM Receiver Circuit |

| W2005BBE | FM Receiver Circuit |

| W2010AAF | RF Modulator |

| W2011 | RF Modulator |

| W2011BBY | RF Modulator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W195B | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Frequency Generator for Integrated Core Logic |

| W195E15 | 制造商:Omron Corporation 功能描述: |

| W195E33 | 制造商:OMRON INDUSTRIAL AUTOMATION 功能描述:CV Series Install. |

| W196 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Spread Spectrum FTG for 440BX and VIA Apollo Pro-133 |

| W196_02 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Spread Spectrum FTG for 440BX and VIA Apollo Pro-133 |

发布紧急采购,3分钟左右您将得到回复。