- 您现在的位置:买卖IC网 > PDF目录140424 > W332M64V-125SBI (MICROSEMI CORP-PMG MICROELECTRONICS) 32M X 64 SYNCHRONOUS DRAM, 6 ns, PBGA208 PDF资料下载

参数资料

| 型号: | W332M64V-125SBI |

| 厂商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分类: | DRAM |

| 英文描述: | 32M X 64 SYNCHRONOUS DRAM, 6 ns, PBGA208 |

| 封装: | 13 X 22 MM, PLASTIC, BGA-208 |

| 文件页数: | 4/15页 |

| 文件大小: | 355K |

| 代理商: | W332M64V-125SBI |

12

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

W332M64V-XSBX

August 2007

Rev. 4

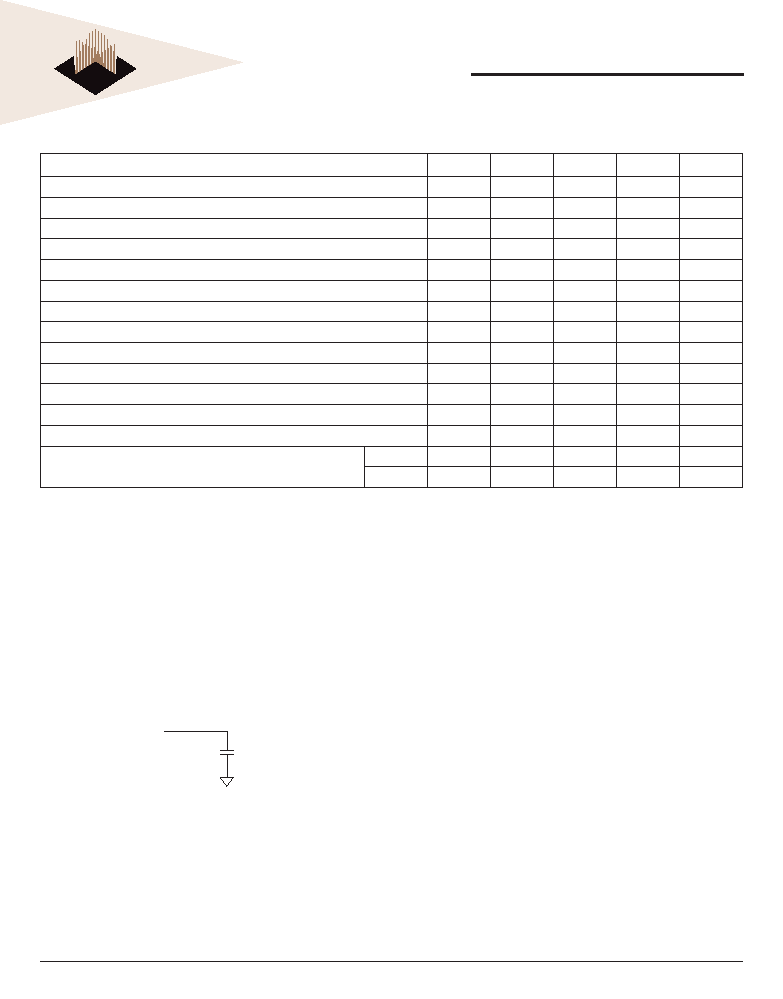

AC FUNCTIONAL CHARACTERISTICS (NOTES 5,6,7,8,9,11)

Parameter/Condition

Symbol

-100

-125

-133

Units

READ/WRITE command to READ/WRITE command (17)

tCCD

111

tCK

CKE to clock disable or power-down entry mode (14)

tCKED

1

tCK

CKE to clock enable or power-down exit setup mode (14)

tPED

111

tCK

DQM to input data delay (17)

tDQD

0

tCK

DQM to data mask during WRITEs

tDQM

0

tCK

DQM to data high-impedance during READs

tDQZ

2

tCK

WRITE command to input data delay (17)

tDWD

0

tCK

Data-in to ACTIVE command (15)

tDAL

455

tCK

Data-in to PRECHARGE command (16)

tDPL

2

tCK

Last data-in to burst STOP command (17)

tBDL

111

tCK

Last data-in to new READ/WRITE command (17)

tCDL

1

tCK

Last data-in to PRECHARGE command (16)

tRDL

2

tCK

LOAD MODE REGISTER command to ACTIVE or REFRESH command (25)

tMRD

222

tCK

Data-out to high-impedance from PRECHARGE command (17)

CL = 3

tROH

333

tCK

CL = 2

tROH

2—

—

tCK

NOTES:

1. All voltages referenced to VSS.

2. This parameter is not tested but guaranteed by design. f = 1 MHz, TA = 25°C.

3. ICC is dependent on output loading and cycle rates. Specied values are obtained

with minimum cycle time and the outputs open.

4. Enables on-chip refresh and address counters.

5. The minimum specications are used only to indicate cycle time at which proper

operation over the full temperature range is ensured.

6. An initial pause of 100μs is required after power-up, followed by two AUTO

REFRESH commands, before proper device operation is ensured. (VCC and VCCQ

must be powered up simultaneously.) The two AUTO REFRESH command wake-

ups should be repeated any time the tREF refresh requirement is exceeded.

7. AC characteristics assume tT = 1ns.

8. In addition to meeting the transition rate specication, the clock and CKE must

transit between VIH and VIL (or between VIL and VIH) in a monotonic manner.

9. Outputs measured at 1.5V with equivalent load:

Q

50pF

10. tHZ denes the time at which the output achieves the open circuit condition; it is not

a reference to VOH or VOL. The last valid data element will meet tOH before going

High-Z.

11. AC timing and ICC tests have VIL = 0V and VIH = 3V, with timing referenced to 1.5V

crossover point.

12. Other input signals are allowed to transition no more than once every two clocks

and are otherwise at valid VIH or VIL levels.

13. ICC specications are tested after the device is properly initialized.

14. Timing actually specied by tCKS; clock(s) specied as a reference only at minimum

cycle rate.

15. Timing actually specied by tWR plus tRP; clock(s) specied as a reference only at

minimum cycle rate.

16. Timing actually specied by tWR.

17. Required clocks are specied by JEDEC functionality and are not dependent on

any timing parameter.

18. The ICC current will decrease as the CAS latency is reduced. This is due to the fact

that the maximum cycle rate is slower as the CAS latency is reduced.

19. Address transitions average one transition every two clocks.

20. CLK must be toggled a minimum of two times during this period.

21. VIH overshoot: VIH (MAX) = VCCQ + 2V for a pulse width 3ns, and the pulse width

cannot be greater than one third of the cycle rate. VIL undershoot: VIL (MIN) = -2V

for a pulse width 3ns.

22. The clock frequency must remain constant (stable clock is dened as a signal

cycling within timing constraints specied for the clock pin) during access or

precharge states (READ, WRITE, including tWR, and PRECHARGE commands).

CKE may be used to reduce the data rate.

23. Auto precharge mode only. The precharge timing budget (tRP) begins 7.5ns/7ns

after the rst clock delay, after the last WRITE is executed.

24. Precharge mode only.

25. JEDEC and PC100 specify three clocks.

26. Parameter guaranteed by design.

27. Self refresh available in commercial and industrial temperatures only.

相关PDF资料 |

PDF描述 |

|---|---|

| W3DG6432V7D2 | 32M X 64 SYNCHRONOUS DRAM MODULE, DMA168 |

| W3EG7234S262AJD3 | 32M X 72 DDR DRAM MODULE, DMA184 |

| W3EG7234S265JD3 | 32M X 72 DDR DRAM MODULE, DMA184 |

| W3EG7266S335BD4IG | 64M X 72 DDR DRAM MODULE, 0.7 ns, DMA200 |

| W3EG7266S403BD4IG | 64M X 72 DDR DRAM MODULE, 0.7 ns, DMA200 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W332M64V-125SBM | 制造商:Microsemi Corporation 功能描述:32M X 64 SDRAM, 3.3V, 125MHZ, 208 PBGA, MIL-TEMP. - Bulk |

| W332M64V-133BC | 制造商:Microsemi Corporation 功能描述:32M X 64 SDRAM, 3.3V, 133MHZ, 219 PBGA, COMMERCIAL TEMP. - Bulk |

| W332M64V-133BI | 制造商:Microsemi Corporation 功能描述:32M X 64 SDRAM, 3.3V, 133MHZ, 219 PBGA, INDUSTRIAL TEMP. - Bulk |

| W332M64V-133BM | 制造商:Microsemi Corporation 功能描述:32M X 64 SDRAM, 3.3V, 133MHZ, 219 PBGA, MIL-TEMP. - Bulk |

| W332M64V-133SBC | 制造商:Microsemi Corporation 功能描述:32M X 64 SDRAM, 3.3V, 133MHZ, 208 PBGA, COMMERCIAL TEMP. - Bulk |

发布紧急采购,3分钟左右您将得到回复。