- 您现在的位置:买卖IC网 > PDF目录276891 > W3E32M64SA-200BI (MICROSEMI CORP-PMG MICROELECTRONICS) 32M X 64 DDR DRAM, 0.8 ns, PBGA219 PDF资料下载

参数资料

| 型号: | W3E32M64SA-200BI |

| 厂商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分类: | DRAM |

| 英文描述: | 32M X 64 DDR DRAM, 0.8 ns, PBGA219 |

| 封装: | 25 X 25 MM, PLASTIC, BGA-219 |

| 文件页数: | 2/17页 |

| 文件大小: | 701K |

| 代理商: | W3E32M64SA-200BI |

W3E32M64SA-XBX

10

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

December 2007

Rev. 1

REFRESH command is initiated like an AUTO REFRESH

command except CKE is disabled (LOW). The DLL is

automatically disabled upon entering SELF REFRESH

and is automatically enabled upon exiting SELF REFRESH

(200 clock cycles must then occur before a READ

command can be issued). Input signals except CKE are

“Don’t Care” during SELF REFRESH. VREF voltage is also

required for the full duration of SELF REFRESH.

The procedure for exiting self refresh requires a sequence

of commands. First, CK and CK# must be stable prior

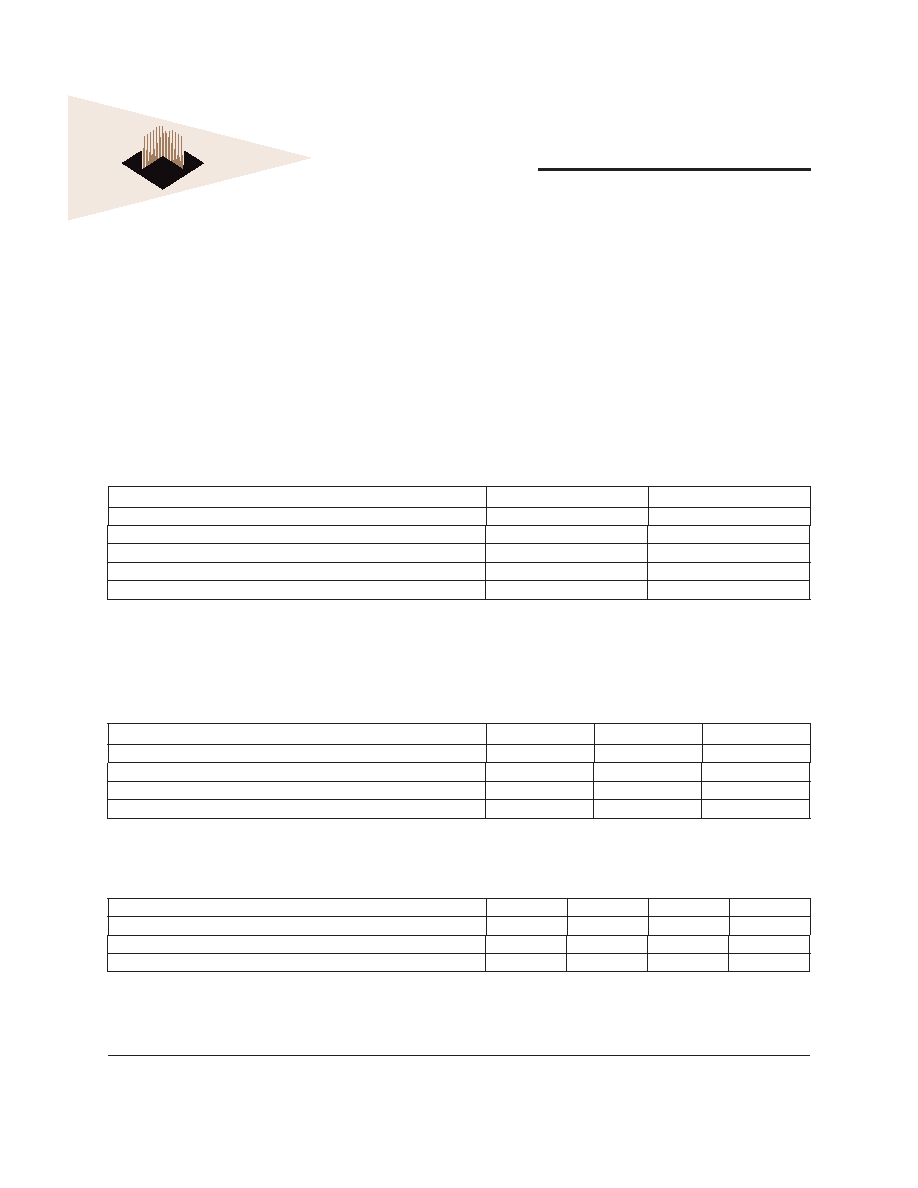

ABSOLUTE MAXIMUM RATINGS

Parameter

Unit

Voltage on VCC, VCCQ Supply relative to Vss

-1 to 3.6

V

Voltage on I/O pins relative to VSS

-1 to 3.6

V

Operating Temperature TA (Mil)

-55 to +125

°C

Operating Temperature TA (Ind)

-40 to +85

°C

Storage Temperature, Plastic

-55 to +125

°C

NOTE: Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of

the device at these or any other conditions greater than those indicated in the operational sections of this specication is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

CAPACITANCE (NOTE 13)

Parameter

Symbol

Max

Unit

Input Capacitance: CLK

CI1

8

pF

Addresses, BA0-1 Input Capacitance

CA

22

pF

Input Capacitance: All other input-only pins

CI2

10

pF

Input/Output Capacitance: I/Os

CIO

10

pF

BGA THERMAL RESISTANCE

Description

Symbol

Max

Units

Notes

Junction to Ambient (No Airow)

Theta JA

14.1

°C/W

1

Junction to Ball

Theta JB

10.0

°C/W

1

Junction to Case (Top)

Theta JC

5.2

°C/W

1

NOTE 1: Refer to "PBGA Thermal Resistance Correlation" Application Note at www.whiteedc.com in the application notes section for modeling conditions.

to CKE going back HIGH. Once CKE is HIGH, the DDR

SDRAM must have NOP commands issued for tXSNR,

because time is required for the completion of any internal

refresh in progress.

A simple algorithm for meeting both refresh and DLL

requirements is to apply NOPs for tXSNR time, then a DLL

Reset and NOPs for 200 additional clock cycles before

applying any other command.

* Self refresh available in commercial and industrial temperatures only.

相关PDF资料 |

PDF描述 |

|---|---|

| W3EG72256S265JD3MF | 256M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3EG7232S202AD4S | 32M X 72 DDR DRAM MODULE, 0.75 ns, DMA200 |

| W3EG7232S202BD4IMG | 32M X 72 DDR DRAM MODULE, 0.75 ns, DMA200 |

| W3EG7232S262AD4ISG | 32M X 72 DDR DRAM MODULE, 0.75 ns, DMA200 |

| W3EG7232S265BD4SG | 32M X 72 DDR DRAM MODULE, 0.75 ns, DMA200 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3E32M64SA-200BM | 制造商:Microsemi Corporation 功能描述:32M X 64 DDR, 2.5V, 200 MHZ, 219 PBGA, MIL-TEMP. - Bulk |

| W3E32M64SA-250BC | 制造商:Microsemi Corporation 功能描述:32M X 64 DDR, 2.5V, 250 MHZ, 219 PBGA, COMMERCIAL TEMP. - Bulk |

| W3E32M64SA-250BI | 制造商:Microsemi Corporation 功能描述:32M X 64 DDR, 2.5V, 250 MHZ, 219 PBGA, INDUSTRIAL TEMP. - Bulk |

| W3E32M64SA-250BM | 制造商:Microsemi Corporation 功能描述:32M X 64 DDR, 2.5V, 250 MHZ, 219 PBGA, MIL-TEMP. - Bulk |

| W3E32M64SA-266BC | 制造商:Microsemi Corporation 功能描述:32M X 64 DDR, 2.5V, 266 MHZ, 219 PBGA, COMMERCIAL TEMP. - Bulk |

发布紧急采购,3分钟左右您将得到回复。