- 您现在的位置:买卖IC网 > PDF目录276905 > WED2DL36513V40BI 512K X 36 MULTI DEVICE SRAM MODULE, 4 ns, PBGA119 PDF资料下载

参数资料

| 型号: | WED2DL36513V40BI |

| 元件分类: | SRAM |

| 英文描述: | 512K X 36 MULTI DEVICE SRAM MODULE, 4 ns, PBGA119 |

| 封装: | PLASTIC, BGA-119 |

| 文件页数: | 2/12页 |

| 文件大小: | 266K |

| 代理商: | WED2DL36513V40BI |

10

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

WED2DL36513V

WED2DL36513AV

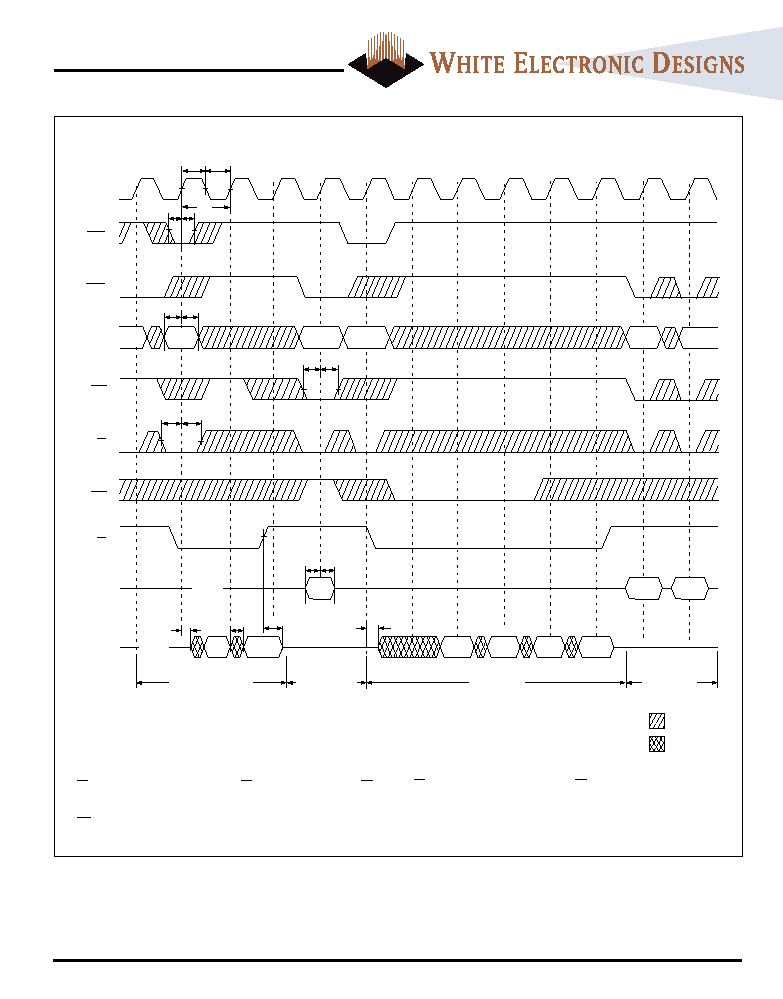

FIG. 5 READ/WRITE TIMING DIAGRAM

ADSP

ADSC

ADDRESS

BWx

(NOTE 4)

CE

(NOTE 2)

tADSS

tADSH

ADV

OE

CLOCK

A2

tAS tAH

Q

tKH

tKL

tKC

tOELZ

Q(A4+2)

Q(A4)

Q(A1)

Q(A4+1)

Q(A4+3)

tKQLZ

tKQ

tOEHZ

Back-to-Back READs

(NOTE5)

SINGLE WRITE

Back-to-Back

WRITEs

BURST READ

Q(A2)

(NOTE 3)

A5

A6

DON’T CARE

UNDEFINED

tCSS tCSH

tWS tWH

(NOTE 1)

HIGH-Z

D

HIGH-Z

A1

A3

A4

(NOTE 4)

D(A3)

D(A5)

D(A6)

tDS

tDH

NOTES:

1. Q (A4) refers to output from address A4. Q (A4+1) refers to output from the next internal burst address following A4.

2. CE2 and CE2 have timing identical to CE. On this diagram, when CE is LOW, CE2 is LOW and CE2 is HIGH. When CE is HIGH, CE2 is HIGH and

CE2 is LOW.

3. The data bus Q remains in High-Z following a WRITE cycle unless ADSP, ADSC or ADV cycle is performed.

4. GW is HIGH.

5. Back-to-back READs may be controlled by either ADSP or ADSC.

相关PDF资料 |

PDF描述 |

|---|---|

| WSF512K16X-72H2IA | SPECIALTY MEMORY CIRCUIT, CHMA66 |

| WF128K32-120G2Q5 | 128K X 32 FLASH 5V PROM MODULE, 120 ns, CQFP68 |

| WF128K32-120G2UQ5 | 128K X 32 FLASH 5V PROM MODULE, 120 ns, CQFP68 |

| WF128K32-150G2UQ5 | 128K X 32 FLASH 5V PROM MODULE, 150 ns, CQFP68 |

| WS256K32L-35HMA | 256K X 32 MULTI DEVICE SRAM MODULE, 35 ns, CHIP66 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| WED2DL36513V-B | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SSRAM MCP |

| WED2EG472512V5D2 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:16MB (4x512Kx72) SYNC BURST PIPELINE, DUAL KEY DIMM |

| WED2EG472512V65D2 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:16MB (4x512Kx72) SYNC BURST PIPELINE, DUAL KEY DIMM |

| WED2EG472512V6D2 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:16MB (4x512Kx72) SYNC BURST PIPELINE, DUAL KEY DIMM |

| WED2EG472512V7D2 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:16MB (4x512Kx72) SYNC BURST PIPELINE, DUAL KEY DIMM |

发布紧急采购,3分钟左右您将得到回复。